基于DSP+FPGA多視頻通道的切換控制

隨著計算機和數字圖像處理技術的飛速發展,視頻監控技術應用廣泛。傳統的視頻監控系統都是用單一攝像頭對某一固定場景進行監控,不僅視頻的視野范圍有限,而且不能對同一個物體的不同方位進行監控。這里提出了一種多通道視頻監控系統,通過對不同視頻通道穩定、可靠地切換控制,實現監控不同場景。該系統不僅彌補了傳統監控視頻范圍有限的不足,而且提高了監控資源的利用率,降低了監控成本。

本文引用地址:http://www.104case.com/article/148235.htm1 系統硬件結構

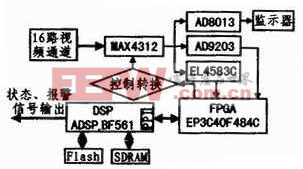

采用DSP+FPGA的硬件結構方案,利用DSP和FPGA控制MAX4312選通所需要的視頻通道,從而達到在多路視頻通道間進行切換的目的。系統結構框圖如圖1所示。

圖1 系統結構框圖

1.1 控制器件的選型

根據實際需要,DSP采用ADI公司推出的Blackfin系列高性能處理器ADSP_BF561(以下簡稱BF561)作為算法處理和控制核心,BF561處理器包含2個獨立的BF533內核,每個內核分別包含2個乘/累加器(MAC),2個40位的ALU,4個視頻ALU和1個40位移位器。Blackfin處理器采用改進的哈佛結構和分級的存儲器結構。L1存儲器一般以全速運行,沒有或只有很少延遲。L2是另一級存儲器,分布在片內或片外,對其訪問會消耗多個處理器周期。在L1級,指令存儲器只存放指令,2個數據存儲器存放數據,1個專用的臨時數據存儲器存儲堆棧和局部變量信息。在L2級,采用統一的存儲空間,可以存放指令和數據。這里采用L2級存儲器。

FPGA采用Altera公司的EP3C40F48C對視頻信號進行預處理,該芯片具有多達24 624個邏輯單元,具有高級外部存儲器接口,允許將外部單數據率(SDR)SDRAM,雙數據率(DDR)SDRAM和DDR FCRAM器件集成到復雜系統設計中,而不會降低數據訪問性能,具有129個兼容的LVDS通道,每個通道數據率高達640 Mb/8,還有4個可編程鎖相環和8個全局時鐘線。另外EP3C40F484C的功耗較低,全局運行時總功耗為300 mW左右。

1.2 Flash的設計

根據系統設計的需要,Flash采用CMOS型的M29W640D,其空間為18 Mx16 bit。該系統中,外部數據線為D1~D15,地址線為A2~A22。連接時需要注意,因為Flash是16 bit位寬,硬件連接上需要地址錯位,即DSP的A2對應Flash的A1,DSP的A3對應Flash的A2,依次類推。在軟件編程上,任何對Flash的操作,如擦除、寫入,均要先對特定地址寫入一定數量固定的控制命令字,即簽到指令,這樣確保在通電和斷電時,不會對存儲器誤操作。

1.3 SDRAM的設計

該系統所采用的外部數據存儲器是大容量SDRAM MT48LC16M16,其容量是4 Bankx8 Mx16 bit。根據該系統設計的實際要求,SDRAM在系統運行時存儲實時圖像數據、基準數據以及程序代碼。由于Flash的存取速度比較慢,在Flash里,在系統初始化時應預先將存儲在其中的基準數據及程序代碼搬到更快的存儲器里面,以便DSP不受存儲器讀取時間的制約,充分發揮其高速性能。

1.4 視頻采集模塊設計

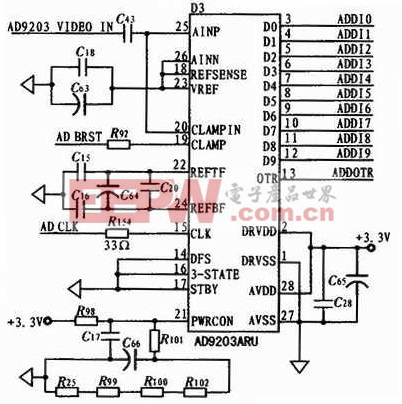

由于視頻通道的切換時間非常短,這就需要切換控制模塊對視頻信號有一個非常準確的判斷,以便及時發送切換命令,因此需要選擇一款高速的轉換器。另外由于本系統的電源為5 V供電,因此需要選擇一款低功耗的器件。因此選擇AD9203作為模擬信號的數字量化器件。

AD9203是ADI公司出品的一款單通道、低電壓的高速A/D轉換器,采樣速率可達40 Ms/s。其精度穩定可靠,在全采樣帶寬范圍內,始終基本保持著10位的精度;在40 Ms/s的采樣速率下,ENOB(有效位數)仍然達到9.55位,差分非線性度±0.25 LSB,信噪比和失真度保持在59 dB左右。AD9203的工作電壓比較靈活,允許住2.7~3.6 V范圍內變動,特別適合于便攜式設備在低電壓下的高速操作。在3 V的供電下,40 Ms/s全速工作時,功耗只有74 mW;在5 Ms/s時,功耗將會降到17 mW,在待機模式下,功耗只有0.65 mW。對于輸入信號的峰峰值,通常設置為1 Vp-p或者2 Vp-p。另外,AD9203允許外部電壓參考,可以根據設計需要,在1~2 V間靈活地設置輸入信號的峰峰值。圖2是AD9203的電路應用原理圖。

圖2 AD9203的電路應用原理圖

2 控制模塊設計

整個系統的工作流程為,在不同的監控點上安裝多個攝像頭進行圖像監控,多路圖像視頻信號通過MAX4312,每一時刻選通其中一路視頻信號輸入。該視頻信號經過AD8013AR處理后從圖像監控器輸出數字圖像信號,同時從行場分離芯片EL4583C輸出相應的行(VIDEO_Hs)、場(VIDEO_Vs)信號,從AD9203輸出圖像后肩信號(AD_BRST)和視頻量化信號。然后將行(VIDEO_Hs)、場(VIDEO_Vs)信號送進DSP,將后肩信號(AD_BRST)和視頻量化信號送進FPGA。FPGA利用這些信號對圖像進行預處理,然后將處理后的圖像通過PPI口送給DSP中進行算法處理。最后由DSP發送視頻通道切換命令完成不同通道之間的切換,并且將最后處理結果送給報警和狀態指示裝置,實現監控告警功能。軟件控制流程如圖3所示。

評論