基于DSP+CPLD的無刷直流電機三環控制設計

3 系統硬件設計

3.1 DSP芯片

系統選用TMS320F2812型DSP,TMS320F2812實行低功耗設計,I/O引腳電壓3.3 V,內核電壓1.8 V,最高主頻150 MHz,最小指令周期6.67 ns,外部采用低頻時鐘,通過片內鎖相環進行倍頻。SCI外設接口可方便地與上位機進行RS-422串口通訊。

3.2 CPLD

此處選用EPM3128ATE100-10型CPLD,具有2 500個可用門,128個宏陣列,最多可用I/O口為80個,可滿足系統的需要。系統中CPLD主要功能是對電機霍爾位置信號和DSP給出的PWM信號和電機轉向信號進行邏輯綜合處理,產生控制功率管開關的相序,使電機的三相電樞繞組按一定順序導通從而實現對BLDCM的控制。

系統中CPLD另外一個功能是根據電機霍爾位置信號計算電機速度。對于只有一對極的三相BLDCM,每個機械轉子有6次換相,即轉子每轉

過60°機械角都有一次換相。測得每兩次換相的時間間隔為△t,就可根據公式ω=60°/△t計算出兩次換相間隔間的平均角速度。

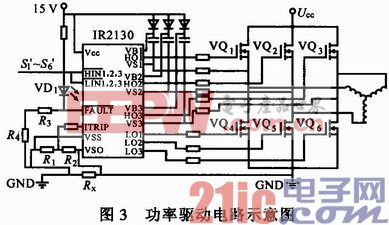

3.3 功率驅動電路

采用三相全橋驅動,上橋臂功率MOSFET管進行PWM的方式控制。功率元件采用N溝道MOSFET管IRF250,驅動元件采用柵極驅動專用電路IR2130,其獨有的HVIC技術使得它可以用來驅動工作在母線電壓高達600 V的電路中的MOSFET器件。

圖3為功率驅動電路示意圖。Rx為電流采樣電阻,對電機電流進行采樣。Rx應選取溫度系數小的電阻,且阻值也應盡量小,系統選用0.05 Ω/4 W的固定線繞電阻。R1和R2構成分壓網絡,采樣信號經過電阻輸入到電流比較器的輸入端ITRIP,當主電路發生過流或橋臂直通(ITRIP端輸入電平高于0.5 V)時,IR2130內部保護電路使其輸出驅動信號全為低電平,從而使被驅動功率管全部截止。故障輸出端FAULT變為低電平,二極管VD1發光報警。FAULT端的輸出經過R3,R4組成的分壓網絡接入DSP的功率驅動保護中斷輸入引腳PDPINTA,PDPINTA是一個下降沿有效的中斷,有效時將事件管理器A的PWM輸出引腳置為高阻態。S1’~S6’為來自CPLD并經過光耦隔離的控制信號。

3.4 其他硬件電路設計

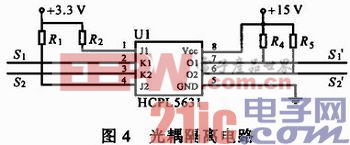

電機在啟動與換向過程中,會產生較大幅度的電流,電機功率供電地會產生較大幅度的毛刺。為了使整個系統具有良好的電磁兼容性,數字電路地與電機功率地應完全分開。

信號地和功率地的隔離由光耦實現,系統選用多路高速光耦HCPL5631。CPLD輸出的6路控制信號經光耦隔離輸入功率驅動電路,如圖4所示。

電流環的組成包括電流采樣與處理。圖3中,Rx對電機電流進行采樣。采樣后的電流值變為電壓值,經過線性光耦,輸入DSP的A/D單元,完成對電流的采樣。

位置傳感器采用電位器,可輸出反映位置信息的電信號,該電信號經過阻容網絡、運算放大器等組成的濾波、放大環節,輸入DSP的A/D單元,完成對位置的采樣。

評論