從硅片到軟件的嵌入系統

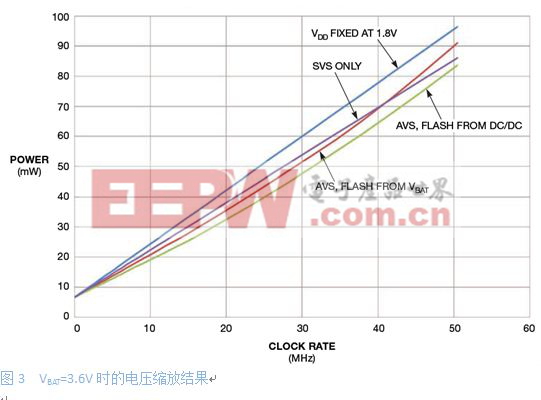

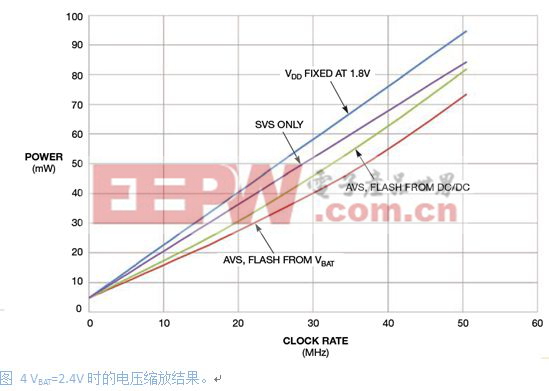

AVS有一個有意思的地方,這就是AVS策略可以根據系統輸入電壓而改變。在本例中,當輸入為3.6V時,用一個高效的內部dc/dc轉換器為內部邏輯以及閃存供電,效率更高。但隨著在產品生命周期內的電池放電,輸入電壓跌落,用輸入電壓為閃存子系統直接供電就成了更高效的方法,因為內部邏輯可以工作在較閃存更低的電壓下。例如,Silicon Labs公司的SiM3L1xx系列MCU就有一個靈活的電源架構,有六個獨立和可變的電源域,能夠實現這種動態的優化。

增加硬件塊(如DMA)可以進一步改變對能耗的折衷。

通常來說,CMOS邏輯電路工作得較慢,因為它們電壓低。如果應用可以容忍較低的性能,則較低電壓可以因能耗中的二次項而獲得大的節能效果,例如常有這種情況,要處理的通信協議,其提交數據的速度不高于某種標準頻率。泄漏為電壓縮放提供了下限。如果每次運行花費時間太長,則泄漏就開始占據能耗方程的主要地位,從而增加了總能耗。因此,執行一個功能越快越好,然后就使處理器回到睡眠模式,盡量減少泄漏成份。

考慮一個需要完成相當多數字信號處理的無線傳感器應用,例如玻璃破碎探測器。在本例中,應用會通過一個快速富利葉變換來分析由音頻傳感器拾取的振動,其特性頻率來自于玻璃的碎裂。FFT比較復雜,因此,如要降低電壓而以較低頻率執行這個變換,就會大大增加泄漏,

即使是采用較老的工藝技術。本例的最佳方案是以接近最高頻率運行這個變換,然后返回睡眠模式,直到要向主結點報告任何結果時。

不過,無線協議代碼會產生不同的要求。射頻協議要求事件有固定的時序。在這些情況下,協議可能要完全由硬件處理。這就使降低處理器核心電壓有了更大的意義。因此,需要做分組組裝與傳輸的代碼要運行在適合于無線協議的速度。

增加硬件塊(如智能DMA)可以進一步改變能耗的折衷情況。很多DMA控制器都需要處理器的頻繁干預,如原生ARM Cortex-M3處理器所提供的DMA控制器。但更多智能DMA控制器能支持一種排隊與鏈接的組合,處理器就可以計算報頭、加密數據、分組組裝,然后以適當的間隔,將數據的傳送工作轉交給緩沖存儲區,供射頻前端使用。在射頻鏈路激活的大多數時間內,處理器可以睡眠,節省大量能源。

存儲器使用。對于現代32 bit MCU,軟件工程師在存儲器塊的使用方式上有高度自由。通常MCU會提供一組存儲器,包括長期保存代碼和數據的非易失存儲器,以及存放臨時數據的SRAM.多數情況下,訪問閃存的功耗要高于SRAM.對于正常使用情況,閃存讀取次數是SRAM讀取數的三倍。閃存寫入消耗的功率更多(需要將整塊擦除,然后用一個相對高電壓脈沖的漫長序列重新寫入)。但對于大多數應用來說,閃存寫入操作并不頻繁,實際上不會影響到平均功耗。

閃存功耗的一個更進一步因素是如何分配來自處理器的存取。每個閃存塊都包含多個頁面,每個頁面的大小最多可達4k字節。要支持存取,每個頁面都必須加電;未被使用的頁面則可以維持在低功耗狀態。如果一個定期存取的代碼段要跨兩個閃存頁,而不是全在一個頁面上,則讀取指令相關的能耗就會增加。將跨不同頁面的頻繁存取代碼與數據在內存中重新分配,就可以在一只電池的放電壽命期間節省不小的能量,而不必修改物理硬件。

通常有意義的是復制功能,它更多地使用片上SRAM而不是閃存,無論是讀還是寫,雖然這種方法看似是對存儲容量的低效使用。電池長壽命的優點可以輕易抵消掉更多的內存消耗。

代碼優化。能量優化亦可以顛覆傳統的代碼效率概念。幾十年來,嵌入系統工程師很注重針對存儲器大小來優化代碼,除非性能是壓倒一切的指標。能量優化提供了另一種全新的度量標準集。一個重要的考慮是采用32 bit平臺上已經普遍提供的片上緩存。

對代碼大小的優化能夠在緩存中保存更多的可執行代碼,從而提高了速度和節省了能耗。不過,函數調用與分支(可重新使用公共代碼,從而減少應用的尺寸)會在同列緩存的代碼段之間造成不可預期的沖突。這樣當需要從主內存中獲取指令時,會造成浪費的“緩存顛覆”,以及多閃存頁激活。

在產品生命周期內要頻繁工作的那些代碼,可以充分壓縮到能裝入緩存中,而不做分支或調用函數,這是有意義的。考慮一個煙霧報警器:即使報警器每周觸發一次(也許源于廚房活動所產生的過多煙氣),也僅是報警器十年壽命中3.15億次事件中的520個。絕大部分時間中,代碼只要讀一下傳感器值,然后發現其未超閾值,就讓處理器核心返回睡眠狀態,等待系統定時器的喚醒。

在警報器獲取的所有傳感器讀數中,只有不到0.0002%的情況才會執行警報生成代碼。余下99.9998%的代碼執行都是核心傳感器讀取循環;確保這個代碼直接在一個緩存列中執行,就成為最低能量使用的關鍵。其它代碼由于運行得極少,可以使用更傳統的技術做優化。

能效工具。對于MCU平臺的能效最大化,工具的支持十分重要。要將不同函數分配到閃存的不同頁,就需要這樣一種鏈接器,它能夠知道目標MCU的存儲器詳圖。鏈接器可以獲得開發人員的輸入結果,看這個塊是否被分配在了跨頁邊界上,并生成已經過非易性存儲最高能效優化的二進制碼。

一般來說,這個代碼也用于確保函數與數據的放置方式,即最常執行的部分不會跨多個緩存列。如果MCU供應商提供了這類工具,則實現這種級別的細節要容易得多,因為他們了解每個目標平臺的存儲器布局與功率需求。而第三方供應商實現這工具則要困難得多。

MCU供應商還詳細地了解不同外設與片上總線的組織方式。這一知識可以用于工具中,指導工程師做出不浪費功率的選擇。

提示

在工藝技術、IC架構以及軟件結構之間的權衡決策,可以得到微妙而有時是無法預期的結果。

電源門控可以減輕泄漏效應,使更先進的工藝結點成為低工作周期系統的較好選擇。

片上穩壓器為設計人員提供了更多靈活性,能夠從一只電池中榨取更多的電荷,而片上dc/dc轉換器與性能監控電路則能實現動態的電壓縮放。

評論