基于PSoC5 DMA的多路輸入與ADC自動控制設計

概述

本文引用地址:http://www.104case.com/article/142465.htm在系統(tǒng)設計中,很多時候會采用多路輸入,分時切換選通進行ADC轉換,可以減少ADC器件的數(shù)量。

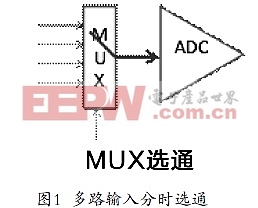

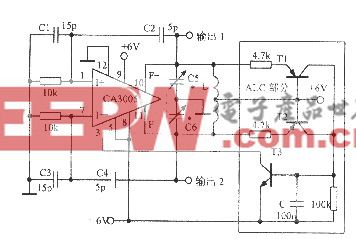

圖1是多路輸入選通的結構圖。目前很多芯片內部已經含有多路選擇器,已經無需外接了。但是對于多路選通的控制,在一般的系統(tǒng)設計中都是需要采用軟件代碼寫寄存器的方式實現(xiàn)。這種方法通常是在ADC轉換完成觸發(fā)中斷,軟件響應中斷,再進行下一路輸入的選通切換。所以,至少需要中斷響應,壓棧,寄存器讀寫,退棧,退出中斷幾個階段。

在這種系統(tǒng)中,如果需要對多路輸入做實時采樣,CPU就需要頻繁響應中斷,主程序任務被頻繁打斷。顯而易見,CPU時間額外開銷會增加;在一些多任務系統(tǒng)中,還會因為需要有任務堆棧保存和切換,影響會更加明顯。并且因為軟件處理周期等原因,延長硬件切換和轉換時間間隔,降低系統(tǒng)工作效率。

Cypress的PSoC5是基于ARM Cortex-M3內核的高性能芯片, 支持0.5~5.5V的寬范圍電壓輸入。更重要的是,PSoC5內含非常豐富的可編程資源UDB(Universal Digital Blocks),以及強大的DMA控制系統(tǒng),可以非常方便地實現(xiàn)對各種外圍資源的讀取和控制。

通過PSoC5的DMA進行結構和配置都非常靈活,可以通過對UDB,SRAM,ADC等資源的操作,實現(xiàn)多路輸入的全自動切換,而不需要CPU響應中斷和軟件干預,無需占用CPU的時間。

在PSoC5中的多路輸入自動切換控制

本設計中以4路輸入,12位精度ADC轉換為例。

在PSoC5中使用硬件MUX,并使用UDB內部的控制寄存器Control_Reg作為MUX的選通控制信號。PSoC5中ADC轉換器的EoC信號(End of Convert)[4] 作為DMA的觸發(fā)信號。

需要使用兩個DMA數(shù)據(jù)流通道,一個是ADC完成轉換(EoC信號有效)后,把ADC中的數(shù)據(jù)寫入SRAM中的buffer[]保存;另一個是把SRAM中的數(shù)組index[]依次寫入到Control_Reg中控制MUX的選通。12bit ADC轉換精度,4路輸入,所以在SRAM中有兩個數(shù)組:uint16 buffer[4]和 uint8 index=[4] {0x0,0x1,0x2,0x3}。

評論