FLIR借助HDL代碼生成技術加速熱成像FPGA的開發

MathWorks 于本日宣布,FLIR Systems 通過使用 MATLAB 和 HDL Coder,將熱成像 FPGA 開發過程中從概念的形成到構建可在現場測試的原型的時間縮短了 60%。通過使用 MATLAB 來設計、仿真和評估算法,并使用 HDL Coder 在 FPGA 上快速實現最佳算法,FLIR 成功加快了開發進程,僅用數小時便強化原有功能并將代碼重新用于原型設計和生產,而不必耗費數周的時間。

本文引用地址:http://www.104case.com/article/136526.htm借助 MATLAB 和 HDL Coder,FLIR 的算法工程師可以自行生成 FPGA 原型,無需為可能并不完全了解相應算法的硬件工程師提供書面說明文檔。這種新的熱成像算法開發工作流程還可消除將算法手動轉換成 HDL 的過程中容易出錯的步驟,使開發人員有更多的時間來更多地嘗試設計迭代。這樣,FLIR 算法工程師就能夠探索各種不同的設計方案,從而對最終原型充滿信心,并將代碼重新用于生產。

FLIR Systems 的圖像處理技術經理 Nicholas Hogasten 表示:“借助 MATLAB 和 HDL Coder,我們能夠更快地對市場需求做出響應。現在我們之所以能夠坦然應對各種變局,原因在于我們可在數周內將新的創意引入具有實時性能的硬件原型上。工程設計過程有了更多樂趣,工作滿意度和客戶滿意度也因此得到提升。”

MathWorks 的 HDL 技術市場經理 Sudhir Sharma 指出:“為了快速準確地開發 FPGA,算法工程師們需要一個有利的環境來促成從理念到實現的迭代設計過程。現在,借助 HDL Coder,算法工程師們只需遵循由按鈕構成的工作流程,即可在 FPGA 上對其 MATLAB 和 Simulink 算法進行原型設計和驗證。”

有關 FLIR Systems 采用 MATLAB 和 HDL Coder 的詳情,請參看用戶案例“FLIR 加快熱成像 FPGA 的開發”。

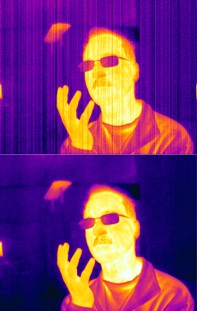

圖注: 原始圖像(頂端)和應用濾波器(通過 HDL Coder 開發而得)后的圖像(底端)

評論