采用低功耗28-nm FPGA降低系統總成本

Altera系統設計工具降低了總體擁有成本

本文引用地址:http://www.104case.com/article/136063.htmAltera的集成設計環境,包括Quartus II軟件,為FPGA業界提供最先進的工具集,降低了開發成本,縮短了產品面市時間。采用Quartus II軟件,從概念構思到產品,您能夠迅速高效的設計整個FPGA。它提供類似ASIC的時序收斂工具(TimeQuest時序分析器),支持很多在系統調試功能。其高效能特性包括,Qsys系統集成工具、系統控制器、收發器工具包,以及DSP Builder和SoC虛擬目標軟件平臺。

采用Qsys實現系統集成

Qsys是下一代SOPC Builder工具,用于幫助設計人員構建并調整系統。Qsys支持用戶開發的以及商用IP模塊的快速集成,加速了您的設計流程,提高了效能。而且,Qsys支持分層設計,簡化了大規模設計的管理,例如,很容易實現并測試具有數百個元件的系統,并且可以管理,方便進行設計重用。基于芯片網絡體系結構,以及自動流水線,其按鍵式性能互聯比SOPC Builder提高了2倍。最終,Qsys幫助設計人員縮短了數月的開發時間,在幾天而不是幾星期內實現PCIe等內核。

通過系統控制臺進行系統研究和調試

利用系統控制臺這一工具,用戶可以使用系統級會話功能,通過方便簡單的軟件應用編程接口(API),在命令行或者系統控制臺圖形用戶界面(GUI)中,采用腳本,或者交互式運行,在更高的抽象級上實時調試FPGA。系統控制臺非常適合電路板開發等任務,使設計人員能夠通過JTAG或者TCP/IP來使用和控制FPGA硬件,從而節省了數星期的時間。

采用具有高級模塊庫的DSP Builder進行DSP應用設計

利用DSP Builder,您可以采用世界上最知名的DSP設計工具MATLAB® Simulink®來設計FPGA。采用這一設計工具,您能夠繼續停留在自己熟悉的EDA環境中,使用易于理解的原理圖輸入工具進行設計,針對目標Altera FPGA自動生成可綜合RTL代碼。您甚至可以直接從MATLAB環境中,在Quartus II軟件中編譯設計,不需要預先學習Verilog或者VHDL便能夠開發FPGA設計。相對于個人和FPGA設計專家的投入,從工程系統級(ESL)設計環境到FPGA設計環境的無縫集成能夠節省設計團隊大量的投入。

DSP Builder為Simulink提供兩種主要插件,基本模塊庫和高級模塊庫,支持您拖動組件,把它們鏈接在一起,并進行仿真。兩種模塊庫都支持您將可綜合組件放到Simulink原理圖瀏覽器中。采用高級模塊庫,DSP Builder會自動對您的數據通路進行流水線處理,滿足您的fMAX目標要求,盡可能重新使用模塊。

SoC虛擬目標

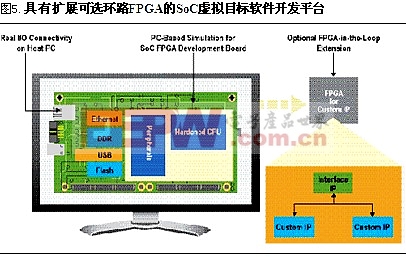

Altera SoC FPGA虛擬目標是對Cyclone V SoC FPGA中的雙核ARM Cortex-A9 MPCore嵌入式處理器開發系統的快速功能仿真。這一全面的原型開發工具“開箱即用”,在PC上運行,啟動Linux操作系統,對實際開發電路板進行建模。虛擬目標與其仿真的實際硬件二進制和寄存器兼容,支持器件專用產品軟件的開發,獲得實際硬件后,不用修改就能夠在硬件中運行。采用虛擬原型開發工具,您可以在具備硬件之前迅速開始軟件開發,進一步提高軟件團隊的效能和軟件質量。

為能夠全面的表示Altera SoC FPGA器件,虛擬目標還采用了基于PC的仿真FPGA擴展功能,名為環路FPGA。如圖5所示,擴展環路FPGA支持虛擬目標與Altera商用FPGA開發電路板的連接,在這些電路板上,您可以實現自己的定制IP,與虛擬目標其他組件一起運行。利用這一特性,您可以采用定制外設和硬件加速器等FPGA硬件來測試您的軟件。

集成實例——采用Cyclone V FPGA的汽車分析

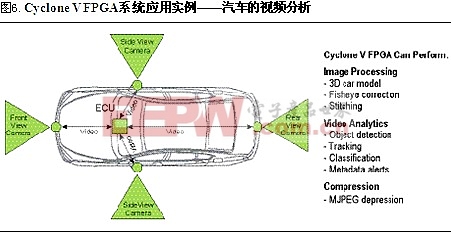

Cyclone V FPGA適用于很多應用。目前發展很快的一種應用是汽車分析。Cyclone V FPGA的低擁有成本以及強大的功能特性非常適合這一應用領域。在進行串行視頻數據處理時,需要進行大量的計算,需要很多存儲器,這都可以利用硬核存儲器控制器、高速串行收發器、fPLL以及豐富的內部邏輯和存儲器資源等硬件特性。

此外,用戶利用Altera的視頻和圖像處理(VIP)包很容易在Qsys中開發復雜視頻處理系統。圖6顯示了汽車中的一個視頻數據集成實例。在這一環境中可以高效的使用Cyclone V FPGA,這是因為它提供了高清晰功能和其他視頻處理特性,例如,縮放和目標探測,不但成本低而且功耗也低。

結論

Cyclone V FPGA降低了總體擁有成本。TSMC的28LP工藝設計用于盡可能降低功耗,同時也是成本最低的28-nm制造工藝。低功耗意味著提高了用戶價值鏈的系統可靠性,延長了系統壽命,降低了運營總成本。此外,Cyclone V FPGA還有很多體系結構優勢,有利于降低系統成本,這包括,硬核存儲器控制器、高效的邏輯和布線資源、fPLL、精度可調DSP模塊,以及最少的電壓軌需求等。而且,Quartus II軟件帶有Qsys和系統控制臺功能、DSP Builder和SoC虛擬目標平臺,支持您高效方便的設計Cyclone V FPGA。對于FPGA設計人員,Altera硅片和設計工具協同工作,實現了最低的總體擁有成本。

評論