STM32-F2系列微控制器

- 有3條內核總線的ARM Cortex-M3內核

- 2個DMA控制器

- 高速 USB主設備控制器

- 10/100以太網 MAC控制器

上圖中的黑點代表在這個7層總線結構中總線主控制器與從控制器的全部接口。為提高系統的能效,SRAM存儲器被分成兩個存儲區SRAM1和SRAM2,SRAM1用于保存基本協議棧和變量,而SRAM2則用作通信外設的幀緩沖區。以太網和USB外設都占用了幾千字節的FIFO存儲空間,而且分別擁有一個各自專用的DMA控制器。

除多個SRAM分區外,該系統還有兩個AHB總線從控制器。同樣地,這樣的配置準許不同的總線主控制器并行處理和同步訪問不同的高速外設,例如,加密處理器和通用輸入輸出端口。AHB從控制器和DMA控制器都是雙端口,這樣設計準許在AHB總線上直接連接DMA控制器與高速外設,避免在總線矩陣和二級高速至低速橋上因延遲而降低性能。

外部存儲器接口又稱“靜態存儲控制器”,可直接連接不同的異步和同步存儲器、NOR/NAND閃存、SRAM、偽SRAM,甚至還能連接一個液晶顯示器控制器,外存接口總線頻率最高60MHz,還能通過指令總線(I-bus)獲取CPU內核指令。

存儲器加速器

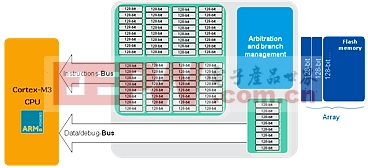

意法半導體的自適應實時(ART)存儲器加速器(如上圖所示)可讓Cortex-M3內核釋放最高的處理性能,雖然閃存本身需要等待狀態,但是,引入這項技術后,STM32-F2以120 MHz的速度從閃存執行代碼無等待狀態。

存儲器接口是128位寬,每次可取4-8條THUMB2指令。如果執行線性代碼,因為預取指功能,即便閃存速度只是內核的四分之一,代碼執行也不會出現等待狀態。

然而,如果執行轉移或跳轉指令,需要立即取出轉移或跳轉目標地址的數據,這樣,存儲器的等待狀態會增加系統開銷,這就是ART及其64項高速指令緩存發揮作用的地方。如果非順序指令第一次出現,這條指令將從存儲器中取出并保存在64項高速緩存的一個存儲項內。在下一次出現時,該指令將從高速緩存中直接取出,沒有等待狀態。

評論