如何讓7系列FPGA的功耗減半

為 FPGA 量身定制的 HPL 工藝

本文引用地址:http://www.104case.com/article/127295.htm在開發(fā)去年推出的 7 系列 FPGA 的過程中,賽靈思評估了多種 28nm 代工工藝,最終選擇與臺積電合作,共同開發(fā)一種專門適用于 FPGA 的工藝。這種名為高性能低功耗 (HPL) 的新工藝采用高介電層金屬閘 (HKMG) 技術(shù),可大幅地降低晶體管的漏電流并實現(xiàn)功耗和性能的最佳組合。賽靈思公司的產(chǎn)品管理總監(jiān) Dave Myron 表示,在 HPL 工藝技術(shù)問世之前,賽靈思和其他 FPGA 公司必須在給定代工廠的低功耗 (LP) 工藝和高性能 (HP) 工藝抉擇。LP 工藝用于性能較低的移動應(yīng)用,而 HP 工藝則是專門為高性能圖形芯片和 MPU 開發(fā)的。

Myron 說:“這兩種工藝對 FPGA 來說都不理想。如果選擇 LP 工藝,性能就是問題,如果選擇 HP 工藝,功耗就會超過預(yù)期。這兩者雖然有回旋余地,但不能滿足我們的需要。”

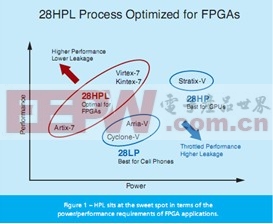

Myron 繼續(xù)道,F(xiàn)PGA 已經(jīng)在大量應(yīng)用中得到廣泛使用,“但它們還不能完全滿足圖形芯片的性能要求以及商用移動電話中的 ASIC 的極低功耗要求。”Myron 說,通過共同研發(fā) FPGA 專用工藝,臺積電和賽靈思找到了兼具高速度和低漏電流的晶體管理想組合。Myron 表示(見圖 1):“采用 HPL,我們能夠定制工藝,使其處于 FPGA 應(yīng)用的性能及功耗要求的理想平衡點上。由于我們的器件能夠不偏不倚地滿足性能-功耗要求,這意味著客戶不必走性能或功耗的極端,從而讓設(shè)計能夠發(fā)揮最大的功效。”

圖 1:HPL 工藝處于 FPGA 應(yīng)用的性能及功耗要求的理想平衡點上

圖中文字:

性能 功耗

專門針對 FPGA 優(yōu)化的 28HPL 工藝

性能更高

漏電流更少

專門針對 FPGA 優(yōu)化的 28HPL 工藝

Virtex-7

Kintex-7

Artix-7

Stratix-V

28HP 最適用于 GPU

Arria-V

Cyclone-V

28LP 最適用于移動電話

性能下降

漏電流更高

fpga相關(guān)文章:fpga是什么

評論