2.5D堆疊硅片互聯

摩爾定律認為芯片上的晶體管數量每過18個月就會翻一番,過去20年,不管是和FPGA廠商還是ASIC廠商都在遵循在這個定律的發展,隨著微電子技術更深入地改變人們的生活,摩爾定律似乎成了芯片技術發展的約束-----如何更早地實現裸眼3D電視?如何更快地提升無線通信帶寬?如何實現低功耗高速存儲?沒有更強大的芯片推出,這些愿景從提出到實現需要漫長的時間,現在,賽靈思公司提出的2.5D堆疊硅片互聯SSI)技術有望破除摩爾定律的魔咒,并有望徹底改變IC產業的游戲規則!

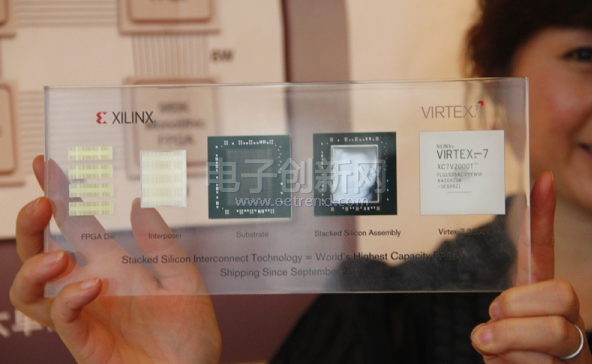

本文引用地址:http://www.104case.com/article/127250.htm今天,賽靈思公司全球同步宣布推出首批28nm Vitex7-2000T FPGA,這是利用2.5D堆疊硅片互聯打造的全球容量最大的FPGA,它有195萬個邏輯門,68億個晶體管,單從晶體管數量上來說它也是世界最大的半導體芯片!它的運算能力是1.5TMACs ,其容量是同類產品的兩倍,這個技術讓FPGA的發展超越了摩爾定律,“這是一個可以game change的技術!”賽靈思全球高級副總裁亞太區執行總裁湯立人評價道。

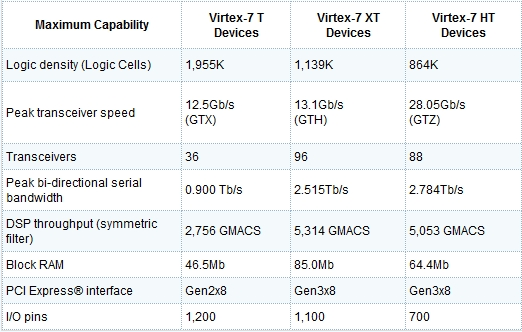

“你可以把它想象成一個巨大的處理平面,它可以處理海量的信息,它有2000個DSP,單個FPGA實現180,000MIPS指令,它就像一個超級計算機!而它的功耗只有19W!”賽靈思公司產品市場營銷總監Brent Przybus強調。“未來我們還會推出針對某些特定應用的版本,例如我們已經推出了Virtex-7 XT和Virtex-7 HT,它們分別增加了高速收發器的數量,峰值帶寬超過2.5Tbps!”

這一強大的FPGA讓許多需要2年后完成的酷炫產品提前面市了!“例如目前大家看好的全視角裸眼3D電視技術,這種全視角裸眼3D需要電視分析觀看者的視角,然后對內容針對視角進行處理,現在還沒有強大的ASIC可以處理這些海量信息,但是Vitex7-2000T的推出,讓實現不在遙遠。”湯立人指出,“預計明年初就將有真正全視角3D裸眼電視推出了。”

他舉例稱,有某無線廠商3年前規劃產品時,提出的需求是需要2000萬門的ASIC,性能要達到Tb級別、功耗預算為30瓦,開發時間為2年,但是,現在3年過去了,該產品的開發現狀是采用多芯片方案,不但需要ASIC,更需要兩塊Virtex-5完成處理,而且功耗高達70瓦!這還沒有計算因項目延長造成的資金投入和市場損失,“如果采用Vitex7-2000T FPGA,同樣可以完成規劃目標,但是功耗要低于30瓦、而開發時間僅為ASIC的1/3!上市時間等于縮短了2年!這給廠商帶來的好處大家都可以想象到!” 湯立人強調,“所以Vitex7-2000T FPGA推出后廣受客戶歡迎,目前我們有2000個design in !而且已經有基于Vitex7-2000T的產品出貨了!”

賽靈思Vitex7產品特性一覽

2.5D芯片堆疊與3D芯片堆疊的糾結

3D芯片堆疊的概念已經提出了很多年,但是如何實現3D芯片一直是產業在探討的難題,目前,真正實現3D芯片的只有mems芯片,“我們認為從目前的芯片到真正的3D芯片還需要數年的時間,而2.5D芯片堆疊是個不錯發展方向,會延續很久。”湯立人指出。“而賽靈思能完成2.5D芯片堆疊,也是得益于其獨特7系列獨特的架構,這種架構可以支持FPGA進行方便的伸縮,如果沒有這種獨特的架構,很難采用這種堆疊互聯技術。”

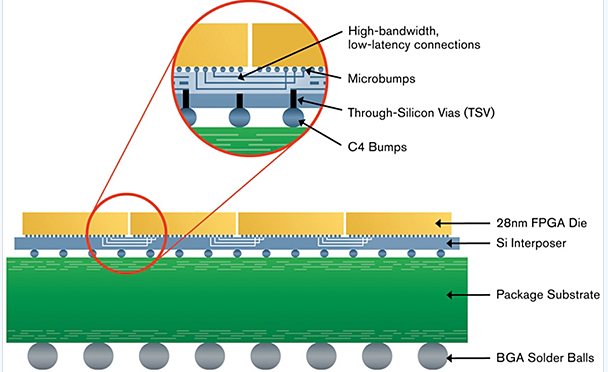

所謂2.5D是指在無源器件上堆疊有源芯片,而3D芯片是指在有源芯片上堆疊有源芯片,賽靈思打造的2.5D堆疊技術是在無源硅中介層上并排幾個硅切片(有源切片),該切片再由穿過中階層的金屬連接,中介層在每個芯片間提供10000多個高速互聯,這與PCB上不同IC通過金屬導線互聯通信類似,這個架構的特點是,Vitex7-2000T雖然有4個切片組成,但設計人員功過賽靈思的設計工具可以將其看作一款大型FPGA進行操作和開發。

堆疊硅片互聯技術封裝示意圖

很多人擔心由此引發的熱管理問題,對此,湯立人解釋說由于中階層是無源的,所以除了FPGA芯片本身有功耗外沒有其他熱問題,它其實就是一個單芯片器件,不用特殊的降溫設計。而由于其內部采用AMBA以及AXI4高速互聯總線,內部互聯產生的功耗遠小于四個器件外部互聯方式產生的熱量,所以采用2.5D堆疊技術的FPGA所產生的功耗要遠低于四個單獨器件的功耗。

另外,采用SSI封裝架構的內應力小于同樣大小的單片式倒裝片BGA封裝,因為中介層能有效分解堆積的內壓力,所以這種封裝還提升了芯片的熱機械性能。

湯立人透露賽靈思早在2006年就開始堆疊芯片互聯技術的研發,以后不斷在90nm、65nm、28nm工藝上進行集成和模塊化開發,終于今天正式推出28nm 堆疊工藝技術的FPGA,這真可謂5年磨一劍,而這個技術也為整個半導體產業帶來福音,“2.5D芯片堆疊互聯技術也可以用于其他IC產品,我們認為這個技術會不斷演進下去,直到數年后3D堆疊技術成熟后它還會有自己的生命力。”湯立人表示,“2.5D堆疊技術未來會從目前的同構系統向異構系統發展,這意味著利用堆疊技術可以把不同類型的器件集成進去。在我們的堆疊中,FPGA采用的是28nm工藝,而無源中介采用的是65nm工藝,這意味著什么?顯然,未來,采用2.5D堆疊技術工藝,可以給高工藝的FPGA集成更多其它工藝器件,比如65nm的模擬器件,40nm的memory等等。”

SEMICO更預測FPGA未來會集成標準單元、分立器件、多核處理器、光學器件等等,到那時,FPGA會變成什么? 發揮你的想象力吧!

賽靈思全球高級副總裁亞太區執行總裁湯立人(中)、賽靈思亞太區上銷售與市場總監張宇清(左)與賽靈思公司產品市場營銷總監Brent Przybus(右)

賽靈思亞太區上銷售與市場總監張宇清指出:“Vitex7-2000T FPGA的推出給ASIC原型開發帶來提升,原來64個FPGA完成13個ASIC模擬驗證,而且只能進行10套軟件系統的開發,而現在只要16個Vitex7-2000T FPGA就可以完成13個大型ASIC模擬驗證,并進行200套系統軟件開發,這在ASIC設計效率的提升是非常驚人!”這其中有趣的現象是ASIC的設計效率提升得益于FPGA的發展,而FPGA又在不斷取代高端ASIC,“因為隨著工藝的演進,高端ASIC的風險和成本驚人,例如28nm的NRE費用就達4000萬美元,這還不算芯片修改的費用,而用28nm FPGA, NRE費用是零!”張宇清舉例道,“另外,ASIC和FPGA各有其發展市場,也不能對立的看待,不能用簡單的取代來看兩個產品。”

前天,臺積電宣布28nm工藝正式量產,共有5家廠商量產,其中FPGA廠家就有兩家,隨著工藝技術的高速發展,一個以FPGA為引領者的時代到來了!

評論