Xilinx FPGA的Fast Startup

系統分區

本文引用地址:http://www.104case.com/article/125814.htm對于這種情形,系統分區是顯而易見的。我們把我們ECU設計分成作為高優先級分區的系統處理器部分和作為低優先級分區的應用處理部分。

這種設計與Virtex-6設計存在很多相似之處,但不同的是,我們用SPI取代BPI作為外置閃存的接口,因此必須用CAN控制器取代TFT控制器。上電后,系統控制器只有有限的時間引導并準備好處理第一個通信數據。由于ECU使用CAN總線用于通信,這個引導時間一般限制為100毫秒。按照傳統配置方法,使用帶低成本配置接口(如SPI或Quad-SPI)的大型Spartan-6很難達到如此嚴格的時序要求。而使用速度更快、更加昂貴的配置接口在汽車領域中是無法接受的。

測量裝置

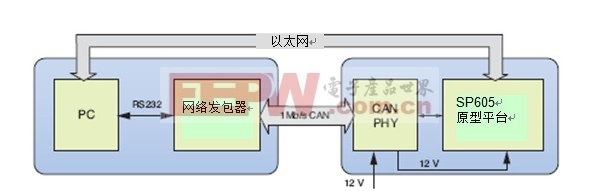

對于SP605汽車ECU演示來說,我們在實驗室中進行了測量,圖6給出了測量裝置。圖中左側是一個基于Spartan-3的X1500汽車平臺,它實現了針對CAN總線的網絡發包器,該發生器能夠收發CAN消息并使用硬件計時器測量CAN消息之間的時間。右側為目標平臺,它沒有直接與CAN總線相連,而是使用來自額外的定制電路板的CAN收發器。除了提供一個CAN PHY之外,這個定制電路板還要控制目標電路板的電源。

圖6 – 汽車ECU的測量裝置

測量配置時間的程序從網絡發包器處于空轉(空檔)狀態下開始,此時CAN PHY電路板上的CAN收發器也處于睡眠模式,SP605也與電源斷開。接著,網絡發包器啟動一個硬件計時器并發送一條CAN消息。識別CAN總線上的事件后,CAN PHY被喚醒并重新讓SP605接通電源。然后FPGA開始載入來自SPI閃存的初始比特流。

由于沒有接收器確認由網絡發包器發送的消息,這條消息立刻重復發送,直至FPGA已經完成其配置并用有效的波特率配置了CAN內核。一旦Spartan-6設計的CAN內核確認了這條消息,網絡發包器的CAN內核將觸發一個中斷,由這個中斷停止硬件計時器。該計時器現在保存著SP605設計的引導時間。測量結果包括SP605設計內一個額外的硬件計時器,此結果表明,當執行該軟件來配置內置BRAM內存的CAN內核時,軟件啟動時間可以忽略不計。

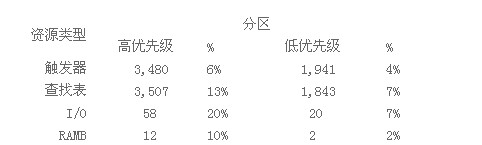

表3表示每個分區的FPGA資源消耗。百分比信息是用來表示使用的XC6S45LXT器件的有效資源的總數量。

表3 – Spartan-6設計中占用的FPGA資源

表4 – 測得的Spartan-6配置時間

評論