用于高速ADC的串行接口

對于高速數據轉換器的串行接口來說,目前有兩種選擇:第一種選擇是串行時鐘-數據-幀(CDF)接口,該接口整合了串行化LVDS(低壓差分信號)數據流以及差分時鐘和幀時鐘,其中差分時鐘用于準確地收集數據,幀時鐘用于建立數據采樣的邊沿。第二種選擇是采用JESD204標準,在該標準中,時鐘嵌入到Gbps級高速雙線串行數據流中。這兩種接口均有各自的優缺點。由于用來驅動高速JESD204接口的電流模式邏輯對(CML)需要較大的功率,所以串行LVDS是實現功率較低且有大量通道的便攜式設計的首選。但是在串行LVDS不適用的場合,JESD204接口就可以發揮作用。

本文引用地址:http://www.104case.com/article/125191.htm串行LVDS的優勢

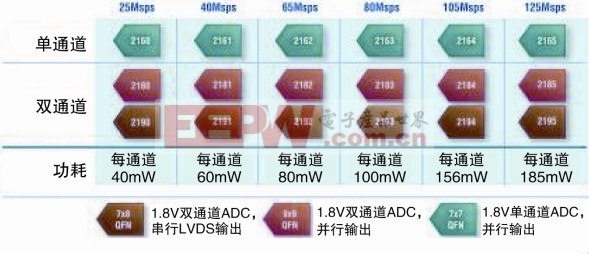

串行LVDS輸出格式減少了ADC和FPGA之間所需的數字I/O數量,節省了FPGA引腳、電路板面積和成本。此外,通過在數據轉換器上采用串行接口,數據轉換器所需的引腳數量也大大減少了,從而可實現尺寸小得多的封裝尺寸。這種優勢在有多通道的設計中得到了充分的顯現。采用串行LVDS接口還是采用并行接口則取決于應用能否承受較大的功耗,以及FPGA是否有能力處理高速數據流。LTC2195是一款16位、125Msps雙通道ADC,具串行LVDS輸出,每通道功耗僅為216mW。不過,與使用雙通道并行輸出版本LTC2185(參見圖1中的完整產品系列圖)相比,串行LVDS接口每通道多消耗31mW功率。這個16位高速ADC系列提供了卓越的76.8dB基帶SNR性能以及90dB SFDR,同時在使用1.8V電源時,功耗非常低。

圖1 凌力爾特的16位低功率、高速ADC系列

就高速ADC而言,協調數據時鐘、幀時鐘和數據時,通常發送器和接收器均需要一個鎖相環(PLL),以正確協調數據時鐘。在GHz速率時,這種協調非常困難,而且數據傳輸速率主要受到接收器的限制。所以,在高于1GHz時,一般不采用這種6線串行發送方法,從而限制了ADC的速率或說限制了ADC的分辨率。

評論