手把手課堂:簡單MicroBlaze微控制器的理念

軟件應用設計流程

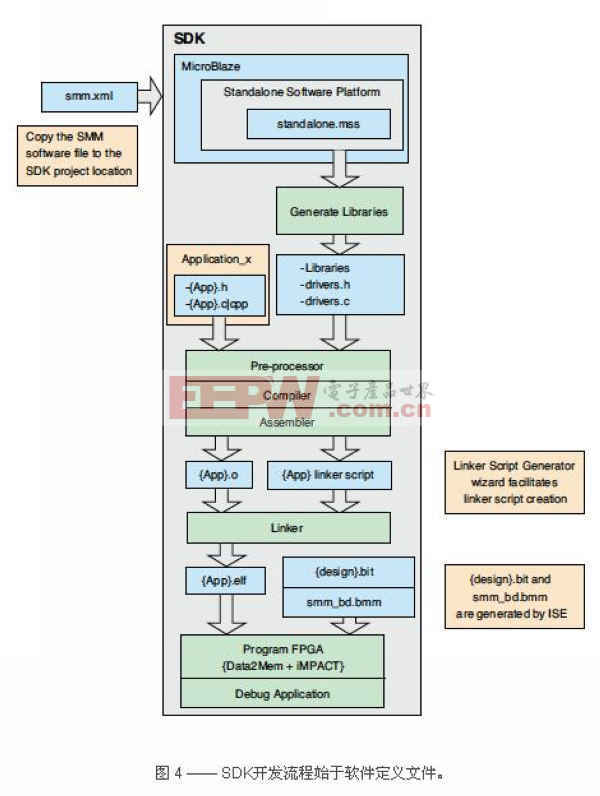

本文引用地址:http://www.104case.com/article/119296.htm單個軟件描述文件 (smm.xml) 包含了啟動微控制器應用開發工作所需的全部信息。開發可獨立于FPGA設計流程進行,甚至在任何FPGA設計實施之前就能啟動。

從ISE 11.1開始,SDK作為獨立選項提供,其包含完成軟件應用設計所需的全部工具、驅動器、程序庫以及實用程序等。

圖4顯示了以軟件定義文件開始的標準的SDK開發流程。微控制器的地址空間包括8KB的RAM與用戶接口,在選擇UART選項的情況下,還包括UART寄存器空間。

您可用C或C++語言編寫軟件應用,并將其存儲于微控制器Block RAM中。此外,RAM空間還可作為微控制器的ROM,因為它可被預載至FPGA比特流中的應用。用戶在配置了FPGA并為微控制器復位解除斷言后,應用就將開始從內部RAM/ROM空間執行。微控制器功能非常完整。

調試選項支持應用的全源級調試,能提供存儲器、寄存器以及變量的直觀視圖。用戶能夠在應用中設置斷點,以更好地開展調試。設計人員可使用與FPGA配置相同的線纜進行調試。完成后就能清除調試選項,以縮小控制器的尺寸。

設計示例

我們不妨來看看一些賽靈思開發板的LCD控制器參考設計,這種設計綜合采用了簡單MicroBlaze微控制器的各種特性。LCD控制器非常適用于小型微控制器實施,因為其硬件接口較慢,也比較簡單,初始化序列較長,而且需要大量字符代碼。

通過綜合采用HDL和C代碼,設計可將消息輸出至電路板上的字符LCD屏。HDL可處理硬件接口,而軟件則負責初始化和控制LCD屏。

LCD模塊的時序較慢,但同時需要指令或數據之間的較大延遲。例如,清空顯示的指令需要1.52毫秒的延遲,然后才能發出下一個指令或數據。部分指令需要40μs的延遲,其它的延遲則需要1μs。

我們可在C語言代碼中用while回路來處理延遲問題,不過這樣做不夠準確,而且還會影響編譯器的優化。更好的選擇

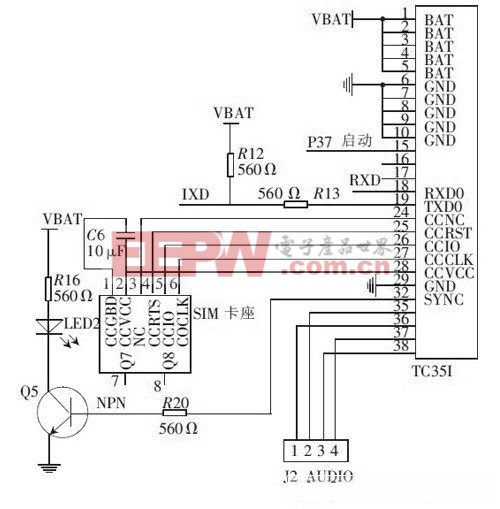

是在FPGA中創建軟件可載入的32位計數器,以便在到達編程的延遲時觸發控制器中斷。MicroBlaze寫入地址0x10,以根據用戶接口數據總線上的數據啟動定時器。MicroBlaze隨后將等待中斷,以繼續執行。

MicroBlaze寫入用戶接口地址0x0會觸發LCD控制器硬件接口,硬件接口的時序由HDL處理。用戶接口數據總線可捕獲指令或數據值。按鈕輸入能夠連接至用戶接口地址0x20。

FPGA設計包括頂級模塊、LCD硬件時序模塊以及軟件可尋址可編程定時器。此外,頂級文件還包括簡單MicroBlaze 微控制器的示例,運行頻率為66 MHz。

C語言應用包含在單個文件中。該代碼不僅可實現MicroBlaze中斷、初始化LCD屏幕、管理不同的延遲情況、打印雙線LCD、等待按鈕輸入,同時還可清空屏幕并輸出新的消息。

在Virtex-6 ML605電路板上,設計所用的FPGA資源還不足1%,并可為設計分區提供更加高效的方式。與僅采用HDL方案的實施和調試相比,C語言代碼的編譯和調試要快一個數量級。

微控制器的定制

由于微控制器采用MicroBlaze構建而成,因此設計人員將能獲得許多標準的外設和選項,以定制嵌入式系統。用戶可能希望部署不同的FPGA架構或添加更多主存儲器、浮點單元或標準的SPI或I2C外設。

定制既定的系統需要EDK。它包括眾多作為嵌入式項目的不同配置,可根據用戶要求進行修改。例如,如果需要16KB的存儲器而不是標準的8KB存儲器,那么用戶可以打開EDK項目,修改MicroBlaze RAM空間并生成新的網表、Block RAM存儲器和軟件描述文件。用戶隨后即可將新的文件添加至ISE和SDK項目中。

誠然,雖然簡單的MicroBlaze微控制器不能滿足所有嵌入式設計的需要,但對于需要簡單微控制器來高效提供控制功能的用戶來說確實是非常好的選擇。此外,其還為希望共享和發布EDK設計的團隊提供了一種定則,那就是無論嵌入式設計的尺寸大小,僅需三個文件就能完成整個實施工作。

c++相關文章:c++教程

評論