手把手課堂:簡單MicroBlaze微控制器的理念

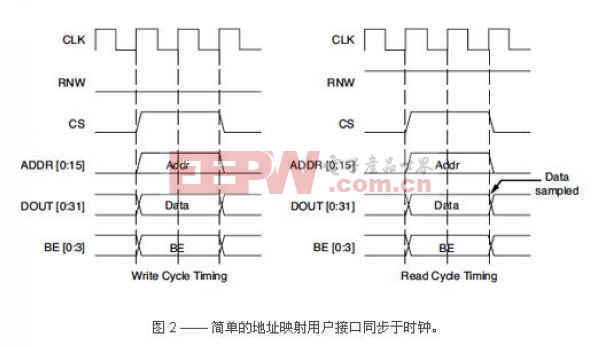

用于可對16位寬的軟件映射地址總線進行解碼,以將不同的定制接口或外設連接至微控制器。在插入片選 (Chip Select) 兩個時鐘周期后對讀取數據進行采樣。

一些預配置的版本可提供串行16450 UART選項。波特率在軟件中進行編程,以保持UART獨立于時鐘輸入。調試選擇可使用內部FPGA資源,并直接連接至FPGA JTAG接口,從而通過常規FPGA下載線纜實現應用調試。

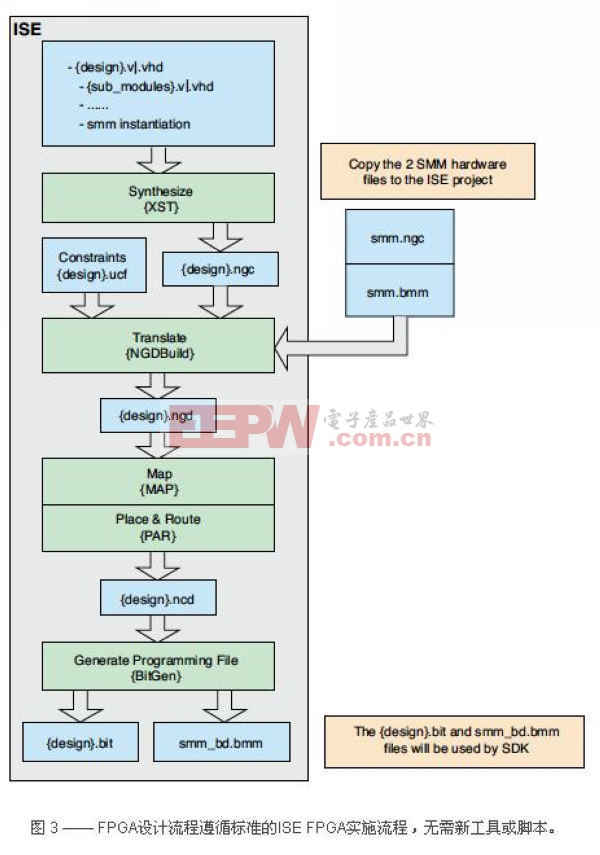

FPGA設計流程

FPGA設計流程遵循如圖3所示的標準ISE FPGA實施流程。您可在FPGA設計中的任何層級級別上通過Verilog或VHDL創建微控制器實例。

使用兩個與硬件相關的文件 —— 微控制器網表 (smm.ngc) 和Block RAM存儲器映射文件 (smm.bmm) —— 即能完成FPGA的實施,用戶既不必費心學習新的工具,也不用使用復雜的腳本流程。FPGA嵌入式設計從未如此的簡單易行。微控制器配置之間的切換非常簡單,只需替換所需的網表文件,然后重新實施FPGA即可。

運行實施工具后, 將額外生成一個文件,指示微控制器所使用 (smm_bd.bmm) 的Block RAM的物理位置。

c++相關文章:c++教程

評論