手把手課堂:Xilinx FPGA設(shè)計(jì)時(shí)序約束指南

作為賽靈思用戶論壇的定期訪客,我注意到新用戶往往對(duì)時(shí)序收斂以及如何使用時(shí)序約束來(lái)達(dá)到時(shí)序收斂感到困惑。為幫助 FPGA設(shè)計(jì)新手實(shí)現(xiàn)時(shí)序收斂,讓我們來(lái)深入了解時(shí)序約束以及如何利用時(shí)序約束實(shí)現(xiàn)FPGA 設(shè)計(jì)的最優(yōu)結(jié)果。

本文引用地址:http://www.104case.com/article/119144.htm何為時(shí)序約束?

為保證設(shè)計(jì)的成功,設(shè)計(jì)人員必須確保設(shè)計(jì)能在特定時(shí)限內(nèi)完成指定任務(wù)。要實(shí)現(xiàn)這個(gè)目的,我們可將時(shí)序約束應(yīng)用于連線中——從某 FPGA 元件到 FPGA 內(nèi)部或 FPGA 所在 PCB 上后續(xù)元件輸入的一條或多條路徑。

在 FPGA 設(shè)計(jì)中主要有四種類型的時(shí)序約束:PERIOD、OFFSET IN、OFFSET OUT 以及 FROM: TO(多周期)約束。

PERIOD 約束與建組

每個(gè)同步設(shè)計(jì)要有至少一個(gè)PERIOD 約束(時(shí)鐘周期規(guī)格),這是最基本的約束類型,指定了時(shí)鐘周期及其占空比。若設(shè)計(jì)中有不止一個(gè)時(shí)鐘,則每個(gè)時(shí)鐘都有自己的 PERIOD 約束。PERIOD約束決定了我們?nèi)绾芜M(jìn)行布線,來(lái)滿足設(shè)計(jì)正常工作的時(shí)序要求。

為簡(jiǎn)化時(shí)序約束應(yīng)用過(guò)程,常常可將具有類似屬性的連線分組為一組總線或一組控制線。這樣做有助于完成正確為設(shè)計(jì)約束定義優(yōu)先級(jí)這一關(guān)鍵步驟。

設(shè)計(jì)約束優(yōu)先次序排列

若設(shè)計(jì)有多重約束,則需進(jìn)行優(yōu)先次序排列。一般來(lái)說(shuō),約束的一般性越強(qiáng),其優(yōu)先級(jí)越低。相反,約束的針對(duì)性越強(qiáng),其優(yōu)先級(jí)越高。舉例來(lái)說(shuō),時(shí)鐘網(wǎng)絡(luò)上的某個(gè)一般性 PERIOD 約束將被特定網(wǎng)絡(luò)的具有更高優(yōu)先級(jí)的 FROM: TO 約束所覆蓋。

特定 FROM: TO(或 FROM: THRU:TO)約束在時(shí)鐘域內(nèi)任意網(wǎng)絡(luò)中的重要性均高于一般性約束。

為便于進(jìn)行約束的優(yōu)先級(jí)排列,可運(yùn)行賽靈思時(shí)序分析器(ISE® Design Suite中的靜態(tài)時(shí)序分析工具),并生成時(shí)序規(guī)格迭代報(bào)告,即常說(shuō)的 .tsi 報(bào)告。該報(bào)告說(shuō)明了各約束間是如何迭代的,以及該工具如何為各約束設(shè)置默認(rèn)優(yōu)先級(jí)。

采用 PRIORITY 約束關(guān)鍵詞可手動(dòng)設(shè)置任一時(shí)序約束的優(yōu)先級(jí)并使其優(yōu)先于默認(rèn)的或預(yù)先設(shè)定的優(yōu)先級(jí)。這對(duì)同一路徑上的兩個(gè)或多個(gè)時(shí)序約束發(fā)生沖突時(shí)尤為有用。這里的優(yōu)先級(jí)指的是同一路徑上有兩個(gè)或多個(gè)時(shí)序約束時(shí),該應(yīng)用哪一個(gè)。其余的低優(yōu)先級(jí)約束則被忽略。優(yōu)先級(jí)可在 -10 ~ +10 的范圍內(nèi)設(shè)置。

PRIORITY 值越低,優(yōu)先級(jí)越高。注意該值不會(huì)影響到哪些路徑應(yīng)率先布局和走線,只有當(dāng)優(yōu)先級(jí)相同的兩個(gè)約束出現(xiàn)在同一路徑上時(shí),它才會(huì)影響由哪個(gè)約束控制該路徑。

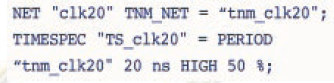

下面將以 PERIOD 只控制從同步元件到同步元件之間的網(wǎng)絡(luò),如 FFS 到FFS 為例來(lái)進(jìn)一步介紹(約束以藍(lán)色顯示如下):

創(chuàng)建名為 tnm_clk20 的 TIMEGRP(時(shí)序分組),包含網(wǎng)絡(luò) clk20 驅(qū)動(dòng)的所有下游同步組件。這些同步元件間的所有路徑均受時(shí)序規(guī)格“TS_clk20: 20ns”(同步元件到同步元件 20 納秒的時(shí)間要求)的約束。“HIGH 50%”指 clk20 的占空比為50/50。

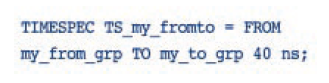

在第二個(gè)例子中,我們使用 FROM:TO 約束來(lái)定義對(duì)兩個(gè)分組間路徑的要求,即:

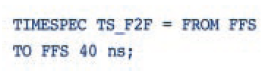

該命令的作用是告知工具,確保數(shù)據(jù)從時(shí)序分組“my_from_grp”包含的元件到“my_to_grp”的元件所用時(shí)間為 40納秒。時(shí)序分析器仍將計(jì)算從源分組到目標(biāo)分組的時(shí)鐘偏移,不過(guò)若時(shí)鐘關(guān)聯(lián),則優(yōu)先級(jí)較低。也可使用如下預(yù)定義分組:

fpga相關(guān)文章:fpga是什么

評(píng)論