全景圖像實時展開在FPGA上的實現

由于ADV7180產生的視頻數據流是隔行掃描數據,分為奇數場和偶數場,所以SDRAM控制器除了對數據流進行存儲,還要在讀取數據時進行去交織操作。SDRAM控制器的雙讀口設計可以出色地完成去交織任務。在讀取數據時,利用VGA的行掃描信號控制這兩個讀口分別讀取:當VGA控制器掃描到奇數行時,由第一個讀口讀取相應奇數行數據;否則,由第二個讀口讀取相應偶數行數據。之后,再合并這兩個讀口讀取的數據得到逐行掃描的、分辨率為640×480的視頻數據流。

本文引用地址:http://www.104case.com/article/117270.htmYCbCr到RGB轉換模塊

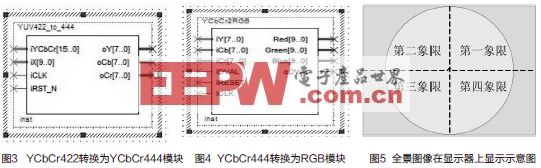

本系統的最終目的是將視頻流輸出到VGA顯示器進行顯示,而從SDRAM讀取得到的數據是YCbCr422格式,不符合VGA顯示要求,所以需要將其轉換為RGB數據格式。

首先將YCbCr422格式轉換為YCbCr444格式。在每一個時鐘上跳沿,判斷當前VGA列掃描信號,若當前列為奇數,則將SDRAM讀口得到的16位YCbCr信號的前8位賦值給Y作為當前像素的Y值,后8位賦值給Cr作為當前像素的Cr值,Cb保持不變;若當前列為偶數,則YCbCr的前8位仍為當前像素的Y值,后8位為當前像素的Cb值,Cr保持不變。這樣就保證了輸出的Y、Cb、Cr三個信號是當前像素的對應描述信號。

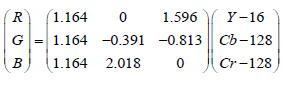

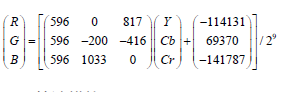

在確定了每個像素對應的YCbCr值之后,就可以通過如下公式計算得到對應的RGB值。

DE2-70上的EP2C70 FPGA芯片內嵌了150個乘法器塊,每一個乘法器塊可以配置為兩個9×9位的乘法器或者一個18×18位的乘法器。所以本系統使用QuartusⅡ中集成的MegaWizard Plug-In Manager配置乘加器模塊用于實現YCbCr顏色空間到RGB顏色空間的轉換。另外,上述轉換公式涉及浮點運算,在Verilog中不易實現,所以將公式中各浮點值左移9位變為整數,從而公式調整為:

???????????−??????????展開算法模塊

???????????−??????????展開算法模塊

展開算法模塊為本系統的核心模塊,利用EP2C70內嵌的M4K存儲器和正余弦生成器實現了極坐標視圖到直接坐標視圖的實時展開。

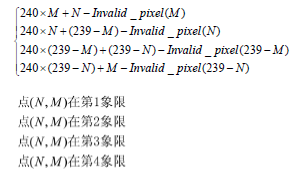

人眼視角約為120°。考慮到人眼觀察的習慣,系統將圓形的極坐標視圖分割成為第一、二、三、四象限四個部分,每部分90°,由使用者選取感興趣的部分進行展開,這樣既符合人眼觀察的習慣,又節省了空間。

視頻分塊

全景極坐標視圖在顯示器上顯示時類似于圖5,其中矩形代表整個顯示器顯示的內容,分辨率為640×480,圓形代表全景圖像出現的位置,半徑大約為240個像素,所以可以按圖5中虛線部分將視頻每一幀分為4塊,每一塊分辨率為240×240。系統使用VGA控制器生成的行列掃描信號標定當前像素的位置,當像素位置位于全景圖像區域內時,則將像素值存入M4K存儲器,否則繼續搜索下一個滿足條件的像素。

M4K存儲器設計

M4K存儲器是內嵌在EP2C70中的存儲器塊,其中每一塊容量達到4096bit,可配置為真雙口存儲器,在EP2C70芯片上共有250塊M4K存儲器塊。本系統使用了209塊M4K存儲器塊,借助其高尋址精度,實現圖像的實時展開。

M4K存儲器寫地址

將數據寫入M4K存儲器時,可以將數據流按照圖像顯示順序全部存入,這樣就需要生成0~360°的所有正余弦查找表;同時,由于存入了全部圖像信息,將會有1/4左右的無效像素點,浪費了寶貴的存儲器資源。系統利用M4K存儲器精確的尋址操作將第二、三、四象限的信息在存入時進行翻轉,使得存入M4K存儲器的圖像僅顯示為第一象限的特性,則只需要生成0~90°的正余弦表就可以完成對整幅圖像的展開計算。其次,固定攝像頭之后,圓形全景圖像在顯示器中的位置是固定的,所以可以確定每一行有效像素的坐標范圍。當行列掃描信號在此范圍之內,則將該像素值存入M4K存儲器中,否則,繼續尋找下一個符合條件的像素點。所以,對第i象限的第M行第N個像素,如果為有效像素,則存入M4K存儲器的地址按如下規則計算:

這里的M和N取值范圍均為[0,239],Invalid_pixel(K)表示在第K行第一個有效像素之前所有無效像素點總數。

fpga相關文章:fpga是什么

色差儀相關文章:色差儀原理

評論