對汽車片上系統采用雙核架構

例如,ALU內的錯誤會造成計算結果不準確,但是只要這些結果只影響內核寄存器值,那么它們就不會對系統運行產生危害。但是,如果這些寄存器被用于某些外部應用,那么就會引起故障。同樣,在SoR內部傳遞的錯誤不會產生直接的危害,比如,如果錯誤的寄存器值被寫入INTC,那么不會對系統的整體行為產生影響。同樣,如果這個被錯誤寫入的INTC寄存器觸發了一次故障中斷,那么系統也會發生故障。

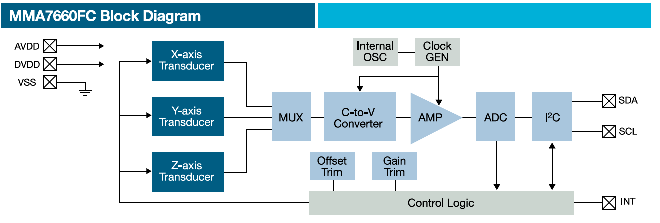

本文引用地址:http://www.104case.com/article/116945.htm冗余校驗器單元將檢查由于外部總線數據在兩個處理單元之間不一致而引起的故障。校驗器單元將檢測這些故障,然后將其傳遞到另一個名為故障收集和控制(FCCU)的模塊。FCCU隨后根據檢測到的故障的性質采取修復操作,并使SoC進入已定義的安全狀態。

去耦并行模式:

在DPM中有兩個獨立運行的相同內核,與之形成對比的是擁有主處理器和協處理器的同構雙核架構,其中協處理器的能力要比主內核更弱一些。這種配置為安全應用中的SoC提供了更高的性能。DPM在硬件層面上沒有針對隨機硬件故障提供內在保護。因此,對于安全應用中使用的DPM,必須在軟件層面上引入一定程度的冗余。這可以通過多種方式實現,例如,采用主校驗器方法,這種方式將運行獨立的檢查軟件,檢查另一個內核中的安全應用是否運行正常。

考慮到嵌入式系統/汽車領域中并不是所有應用都要求具備嚴格的安全性,因此還可以將MPC564xL配置為DPM以增強性能。

DPM相對于協處理器方式的架構優勢:

DPM SoR有一個優點。它有兩組外圍設備,其中包括CPU內核、DMA控制器、中斷控制器、交叉總線系統、內存保護單元、閃存控制器和RAM控制器、外設總線橋、系統定時器和看門狗定時器。這使它擁有比普通雙核系統(處理器和協處理器)更高的性能。

Core0可以使用STM0、SWT0、MPU、MPU等控制應用和訪問從外圍設備。Core1與Core0類似。在復雜應用中,操作系統運行在SoC上,這些冗余配置的外設在控制每個內核上的應用時具有顯著的優勢。

DPM中的每個內核都包括一個RAM控制器和半個RAM陣列。當內核執行不同應用時,堆棧、臨時結果等變量以及每個內核將使用的類似數據都將保存在各自的半個SRAM陣列中。這可以防止由共享引起的內存帶寬瓶頸和故障。

兩個內核都可以訪問兩個AMBA交叉開關,因此很有可能出現其中一個內核阻塞或明顯拖延另一個內核通過交叉開關的情況。這個問題可以通過交叉客戶端中的仲裁優先級解決。

評論