粒子探測器讀出電路數字濾波器設計

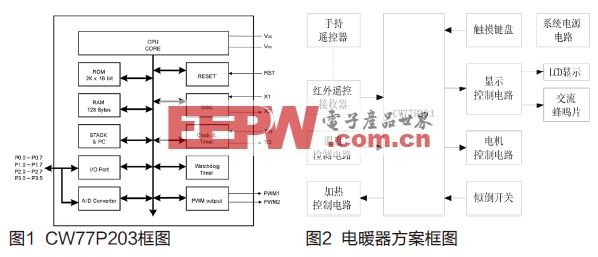

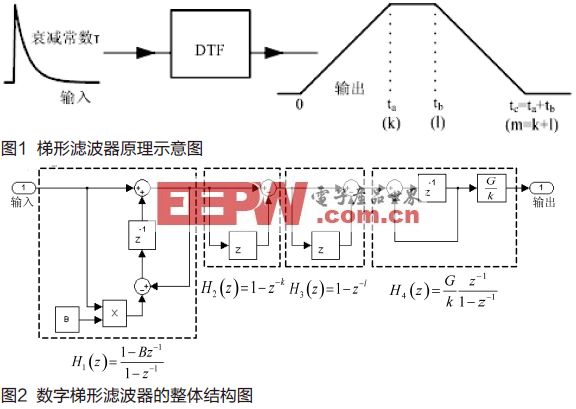

對四個子模塊單獨設計,再級聯就可以得到整個濾波器的整體結構,最終的濾波器整體結構如圖2所示,下面詳細介紹各個模塊的設計。

H1(z)的結構設計

結構設計指的是將線性常系數差分方程描述的系統用加法、乘以系數和延遲等基本運算模塊的互聯所組成的結構來表示。不同的結構,不僅需要的資源是不一樣的,更重要的是,在數值精度有限的時候,它們在性能上可能有很大的差異,這個也是為什么要結構設計的原因。

濾波器的結構有很多形式,例如對于IIR濾波器,就有直接Ⅰ型、直接Ⅱ型以及他們的轉置形式,而這些形式又可以通過級聯和并聯組成更加復雜的結構。這些結構之間的差別在于:

1. 直接Ⅰ型和直接Ⅱ型所需要的延遲單元數目為傳遞函數中分子和分母延遲單元數目之和,而它們的轉置形式所需要的延遲單元數目為分子分母中延遲單元數目的最大者,所以直接Ⅰ型的轉置形式和直接Ⅱ型的轉置形式所需要的延遲單元較少。

2. 直接Ⅰ型的轉置形式和直接Ⅱ型的極點實現在前面,直接Ⅰ型和直接Ⅱ型的轉置形式的則相反,零點實現在前面。實現一個極點相當于積分操作,輸出有可能產生溢出,而零點相當于微分操作,輸出可能產生較大的截斷誤差。這樣,他們的先后次序對系統性能影響很大,需要根據輸入信號的形式選擇零極點的實現次序。

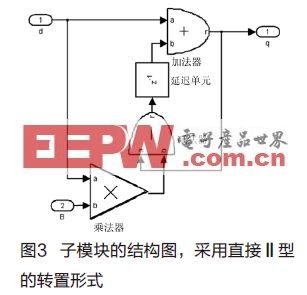

對于()1Hz子模塊,它有一個極點和一個零點,輸入信號是指數衰減信號,如果先實現極點,那么就相當于對輸入的指數衰減信號積分,必然會產生溢出,得到錯誤的結果,所以只能采用先實現零點的方式,也就是選擇直接Ⅰ型或者是直接Ⅱ型的轉置形式,考慮到減小延遲單元的個數,選擇直接Ⅱ型的轉置形式作為()1Hz子模塊的實現結構,得到其結構圖如圖3所示。

延遲數可調的延遲模塊設計

在子模塊H2(z),H3(z)中,都含有延遲數很大的延遲單元kz−,lz−,為了適應不同的噪聲環境,還需要延遲數目k,l是可調的,其實現結構如圖4所示:

如圖4所示,延遲模塊的核心是一個雙口RAM,但是數據不是在寄存器中流動,而是通過改變寫和讀的地址來實現延遲的,它的實現原理可以總結為以下幾點:

● 通過輸入地址計數器控制依次寫入數據;

● 通過輸出地址計數器控制依次讀出數據;

● 延遲單元個數由異步復位時對輸入地址計數器和輸出地址計數器賦初值的差異來確定。

● 由于輸出不能有不確定的值,所以在每一次復位之后,如果輸出地址計數器所指向的存儲單元的值不確定,就輸出0,否則輸出地址計數器所指向的存儲單元的值。這個需要一個復位計數器來控制是輸出0還是 M中的值。

這樣,只需要在復位之前設定 DelayNum的值,就可以在復位的時候對輸入地址計數器和輸出地址計數器賦值來設定延遲單元的延遲數為DelauNum。而且,這樣的實現方式對于降低功耗也是是很有作用的,例如,對于一個延遲數是100的延遲單元,如果采用一般的實現方式,數據在寄存器中流動,那么每個時鐘觸發沿有100個寄存器需要讀寫,而采用上面所用的方式,只需要對兩個寄存器指向的RAM單元讀寫就可以了,雖然增加了一些外圍控制電路,但是開銷相對很少。此外,由于可以采用工藝廠商提供的雙口RAM宏單元,相對于寄存器組實現方式,可以大幅度降低芯片的面積和功耗。

評論