HDLC的DSP與FPGA實現

引言

本文引用地址:http://www.104case.com/article/112019.htmHDLC(高級數據鏈路控制)廣泛應用于數據通信領域,是確保數據信息可靠互通的重要技術。實施HDLC的一般方法通常是采用ASIC器件或軟件編程等。

HDLC的ASIC芯片使用簡易,功能針對性強,性能可靠,適合應用于特定用途的大批量產品中。但由于HDLC標準的文本較多,ASIC芯片出于專用性的目的難以通用于不同版本,缺乏應用靈活性。有的芯片公司還有自己的標準,對HDLC的CRC(循環冗余碼校驗)序列生成多項式等有不同的規定。專用于HDLC的ASIC芯片其片內數據存儲器容量有限,通常只有不多字節的FIFO(先進先出存儲器)可用。對于某些應用來說,當需要擴大數據緩存的容量時,只能對ASIC再外接存儲器或其他電路,ASIC的簡單易用性就被抵銷掉了。 HDLC的軟件編程方法功能靈活,通過修改程序就可以適用于不同的HDLC應用。但程序運行占用處理器資源多,執行速度慢,對信號的時延和同步性不易預測。純軟件HDLC一般只能用于個別路數的低速信號處理。

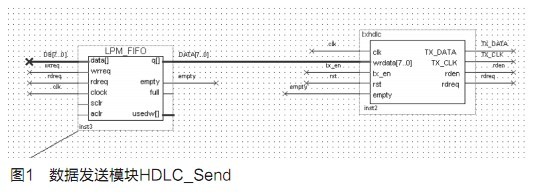

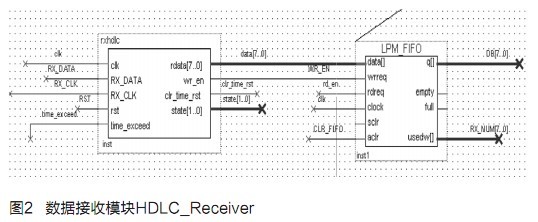

FPGA采用硬件技術處理信號,又可以通過軟件反復編程使用,能夠兼顧速度和靈活性,并能并行處理多路信號,實時性能能夠預測和仿真。

DSP采用軟件技術處理信號,也可以反復編程使用。DSP、FPGA芯片雖成本略微高于ASIC芯片,但具有貨源暢通、可多次編程使用等優點。在中小批量通信產品的設計生產中,用FPGA和DSP實現HDLC功能是一種值得采用的方法。

HDLC的幀結構和CRC校驗

為了使FPGA的設計能夠實現HDLC的基本功能并能按照各項標準的規定靈活采用不同的CRC校驗算法,首先看一下HDLC基本的幀結構形式。

HDLC是面向比特的鏈路控制規程,其鏈路監控功能通過一定的比特組合所表示的命令和響應來實現,這些監控比特和信息比特一起以幀的形式傳送。以下是ISO/IEC 3309標準規定的HDLC的基本幀結構。

其他的HDLC標準也有類似的幀結構。每幀的起始和結束以"7E"(01111110)做標志,兩個"7E"之間為數據段(含地址數據、控制數據、信息數據)和幀校驗序列。幀校驗采用CRC算法,對除了插入的"零"以外的所有數據進行校驗。為了避免將數據中的"7E"誤為標志,在發送端和接收端要相應地對數據流和幀校驗序列進行"插零"及"刪零"操作。

評論