Intersil 推出12位 500MSPS 模數轉換器

全球高性能模擬混合信號半導體設計和制造領導廠商Intersil公司(納斯達克全球精選市場交易代碼:ISIL)今天宣布, 推出全新 8 位、10 位、12 位 500MSPS 模數轉換器系列。12 位的ISLA112P50 IRZ 500MSPS 模數轉換器作為該系列的領銜產品,其功耗僅為 468 毫瓦,比所有12 位 500MSPS ADC 同類競爭產品都低 5 倍。

本文引用地址:http://www.104case.com/article/111603.htm由于在采用ISLA112P50后,系統功耗會大幅降低,因此系統設計人員能夠在單個系統中集成多個 ADC,而且不會出現高性能 ADC 常見的散熱問題。此外,ISLA112P50 的低功耗還能夠在不影響性能的情況下有助于延長電池使用壽命,從而讓便攜式或電池供電應用領域的設計人員受益匪淺。

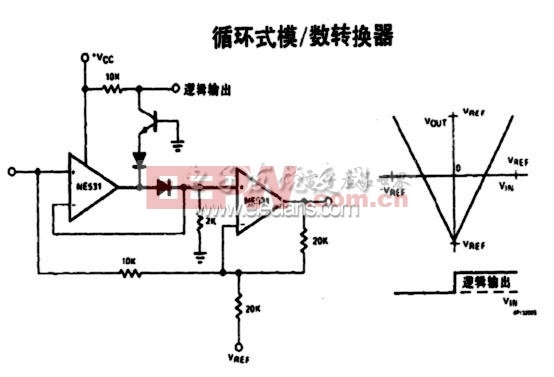

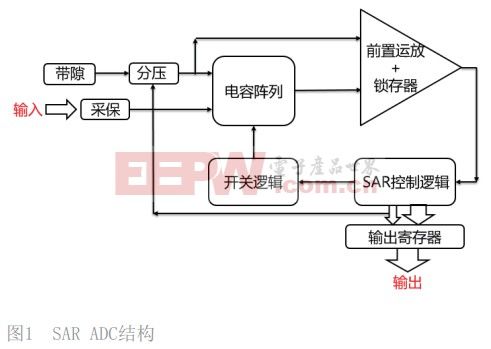

ISLA112P50 是 Intersil不斷擴展的高性能、低功耗 ADC 系列中的最新產品,采用了 Intersil 標準 CMOS 工藝的專有 FemtoCharge 技術,并專門針對寬帶通信、雷達、激光探測及測距系統 (LIDAR) 以及數據采集系統而開發。ISLA112P50 采用一對時序交錯式 250MSPS 單元 A/D 生成 500MSPS 的采樣率。此外,該款 IC 還采用了 Intersil Interleave Engine (I2E) 專利技術,可對偏移、增益以及單元 A/D 之間采樣時間失配進行自動精密校正以確保高性能。

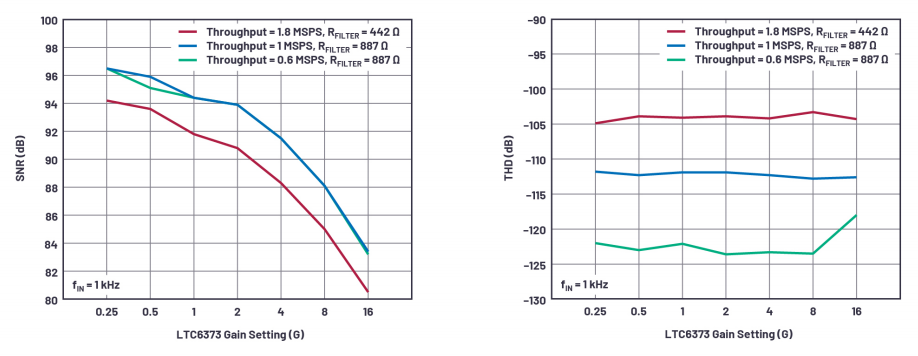

該模數轉換器的動態性能與規范是高端數據采集系統等目標應用的最佳選擇。模擬輸入帶寬為 1.15GHz。輸入頻率為 190MHz 時,信噪比為 65.8dBFS,SFDR 為 80dBc。該產品還融合了打盹/休眠模式,數字輸出數據采用 LVDS 或 CMOS 格式,從而提高了設計靈活性。

同步時鐘分頻器復位協助多器件的時間校準,支持板級交錯或同步采樣,這對某些系統而言是一項非常重要的特性。A/D 輸入時鐘指定的最小/最大接口時序可以使設計人員收斂時序,并選擇性價比最高的 FPGA 來滿足時序要求,從而提高系統可靠性。

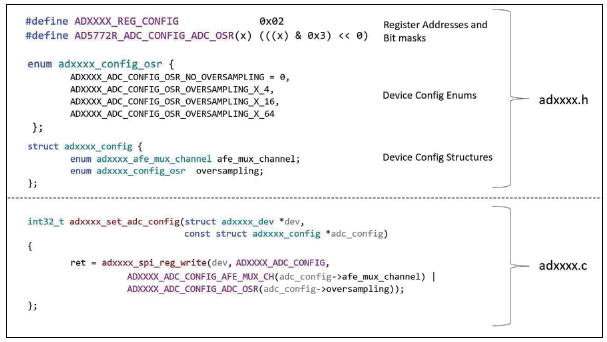

此外,ISLA112P50 還能用串行外設接口端口進行輕松配置,其能控制交錯式校正電路,進而讓系統發出持續的校準命令并配置動態參數。

12 位 ISLA112P50 也是引腳兼容的轉換器系列中的一員,該系列產品包括 10 位ISLA110P50 和 8 位 ISLA118P50。這些產品均采用僅為 10x10mm 的小型 72 引腳 QFN 封裝,與同類競爭產品相比,封裝尺寸縮減了 49% 到 77%。

提供靈活的評估系統

Intersil 還推出了業界最靈活的評估系統,該系統旨在幫助設計人員分析時域和頻域的性能。系統采用模塊化設計,用一個主板支持多個 ADC 系列。Matlab 代碼適用于硬件在環分析,并能夠一次連續捕獲超過 100 萬個采樣。用戶可將捕獲數據下載到標準的 CSV 文件中,并采用專門的后處理技術。

評論