基于Actel FPGA的VGA顯示控制方案

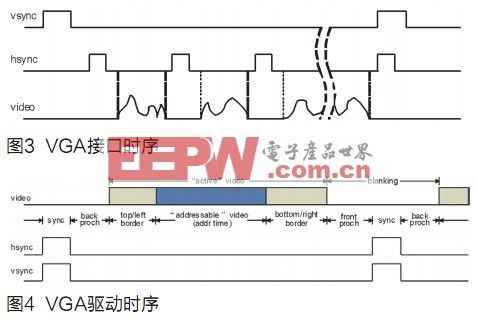

(3).VGA驅動時序

本文引用地址:http://www.104case.com/article/109241.htmVGA的時序不是直接由模擬信號產生的,而是由數字信號控制的,為了將數字信號變成模擬信號,中間要經過D/A轉換處理。VGA接口是沒有數據使能信號的,其顯示是通過行、場掃描的方式實現對顯示器進行掃描控制實現的。所以,VGA的同步信號對時序的要求非常嚴格,如果同步信號沒有同步好,會造成顯示數據的丟失,甚至造成顯示混亂。VGA接口的這些特性,使得在應用中必須由專門的VGA控制器來實現嚴格的VGA驅動時序。

VGA驅動時序中的行、場同步信號的格式是完全一致的,都由同步期sync、同步后肩back proch、同步前肩front proch組成。而像素信號則由頂/左邊框top/left broder、有效像素、底/右邊框bottom/right border組成。不同分辨率下,這些信號是一致的,只是對應的高低電平的保持時間不同。

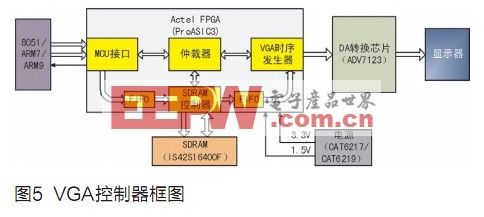

2.控制器框圖

設計采用ProASIC3+SDRAM(IS42S16400F/ IS42S32200F)+DAC(ADV7123)/電阻網絡的方案來實現。用戶可以根據不同的應用場合,選用不同容量的ProASIC3系列芯片,為系統量身打造滿足功能需求且價格便宜的VGA控制器。

評論