CFET技術探索:背面電源與三維堆疊的契合!

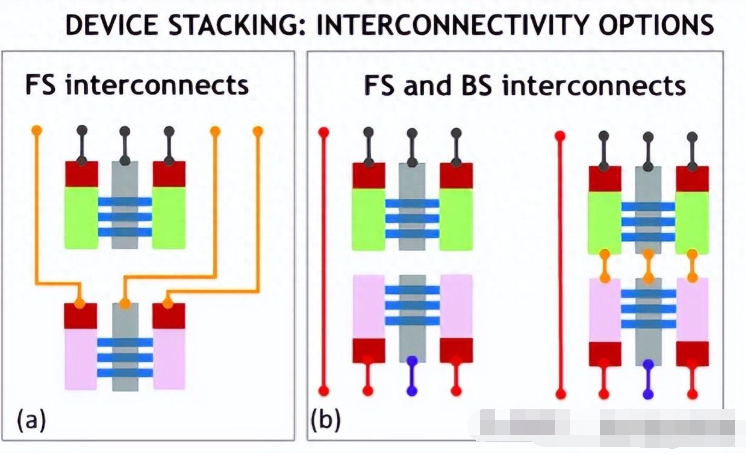

近日,關于CMOS電路中背面電源連接的技術探索備受關注,首個集成背面電源連接的CMOS電路可能采用基于堆疊的納米片晶體管。然而,未來的發展路徑引人關注,規劃者構想了一種新型的互補晶體管(CFET),它將垂直集成堆疊的NFET和PFET器件,為電路設計帶來全新的可能性。

CFET的厚度至少是納米片晶體管的兩倍,這意味著將CFET彼此連接以及與電路其余部分連接將面臨任何互連方案的挑戰,無論是使用背面、正面還是兩者兼用的方案。

在管理中間電介質方面,從CFET的頂部器件到底部電網的接觸需要高寬高比的蝕刻。英特爾將這一過程視為其PowerVia方案的擴展,而不是徹底的改變。然而,與納米片晶體管相比,CFET需要一個中間介電層來隔離NFET和PFET。

根據集成方案的不同,這一層可以在開始時作為Si/SiGe異質結構中的介電層創建,最終形成納米片結構。另外,產生和隔離通道納米片的選擇性蝕刻和氧化步驟也可以為中間介電層產生更厚的氧化物。管理CFET的散熱仍然是一項正在進行的工作。一旦構建了CFET,無論是單片還是順序,下一個大問題是散熱。在芯片層面,背面電源有助于散熱。更粗的電源線電阻更小,并提供一個熱路徑到設備的背面。然而,在任何特定地點,采暖量仍然取決于工作量和當地環境。將器件與背面分開的介電層是熱傳遞的屏障。

即使整體的熱提取是充分的,也可能出現熱點,而沒有大塊硅襯底的熱擴散作用。在12月的IEEE電子器件會議上,Imec的Anabela Veloso及其同事指出,用SiN取代SiO2屏障氧化物可能會改善熱量傳播并降低熱點的風險。

根據英特爾的PowerVia架構,CFET將帶來新的散熱挑戰。添加更多的納米片會降低每一層的電流密度,從而減少加熱,但也會增加電容。通道分裂成平行的納米片降低了散熱,因為中間的介電層是熱傳輸的屏障。盡管增加片數會降低電流密度,但研究表明,積極的縮放會帶來巨大的熱成本。

在電路噪聲管理方面,英特爾的PowerVia架構在前端集成了噪聲屏蔽,以取代信號線之間的隔離效果。

總的來說,背面電源技術和CFET的出現為CMOS電路的發展提供了新的動力和挑戰。未來,隨著技術的進一步發展,背面電源和三維堆疊結構有望成為行業追求更緊湊、更強大系統的關鍵技術。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。