解讀AI大模型推理“芯”機會,RISC-V、一致性總線、WoW的架構創新大有可為。作者 | GACS9月14日~15日,2023全球AI芯片峰會(GACS 2023)在深圳市南山區圓滿舉行。在9月14日AI芯片架構創新專場上,芯至科技聯合創始人、首席芯片架構師兼副總裁尹文分享了主題為《AI計算新時代催生芯片架構走向“算力統一場”》的主題演講。尹文認為,進入AI新時代,算力創新不再僅僅是單個處理器微架構和芯片工藝的創新,而需要軟硬件全棧的系統架構全面創新,未來的創新機會來自以下方面:開放的通用指令架構,高效的融合加速器,異構互聯總線和芯片工程,開源算子庫、工具鏈和軟件。1、AI大模型落地到推理側的新機會與RISC-V架構創新不謀而合,RISC-V不僅可以做標量通用計算,也可以做線程級并行的AI計算。Scaler小標量+SIMT大算力的指令集/微架構融合將是未來RISC-V發力的重點,能以相對低的成本,為AI推理側應用提供高效支持。2、SoC芯片系統的有效算力依賴于計算核心或計算Die之間的高效互聯,通用算力和異構算力需要在整個系統的內存從邏輯上可以被統一為一個更大的具有一致性的空間。低時延大帶寬的一致性總線互聯可以讓異構計算芯片更好更緊密的協同,從而提高整個系統的性能和能效。3、WoW (Wafer on Wafer)混合鍵合在新型芯片工程技術領域有重大價值。在他看來,WoW可將AI Die和Memory Die垂直堆疊,以低于HBM一個量級的成本提供數倍于HBM的帶寬;對于大模型推理來說,4~6GB的Memory Die完全滿足Transformer一層網絡權重的存儲和層內高帶寬需求。基于此,芯至科技圍繞RISC-V開源指令架構、自研一致性總線、WoW 3DIC的架構創新,可以帶來10倍性價比的大模型AI推理芯片。展望更長期的未來,尹文相信基于RISC-V開源指令同構和微架構異構,開源軟件工具鏈及自主一致性總線和芯片工程創新,未來有機會推進到算力統一場。算力統一場將更利于形成更大的自主可控軟件新生態,并符合計算架構的原始特征,助力我國在計算體系方面換道超車。以下為尹文的演講實錄:首先謝謝主辦方的邀請,還有各位同行、各位嘉賓的參與。自從今年上半年大模型層出不窮,從芯片架構領域,各位同行都在一起討論,未來芯片在AI領域的架構怎么做、未來新的機會在哪里。今天我給大家帶來的演講就是我們團隊在這一方面的思考。

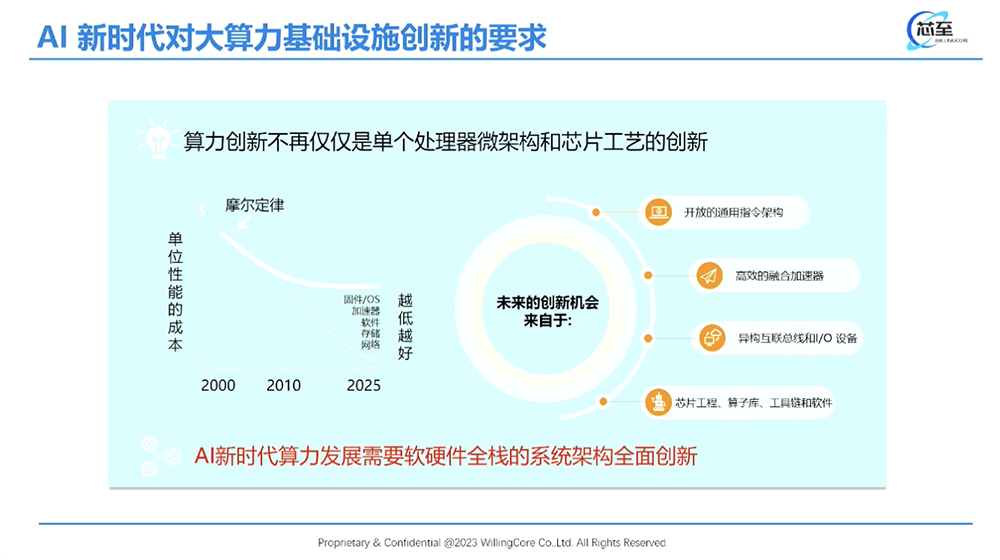

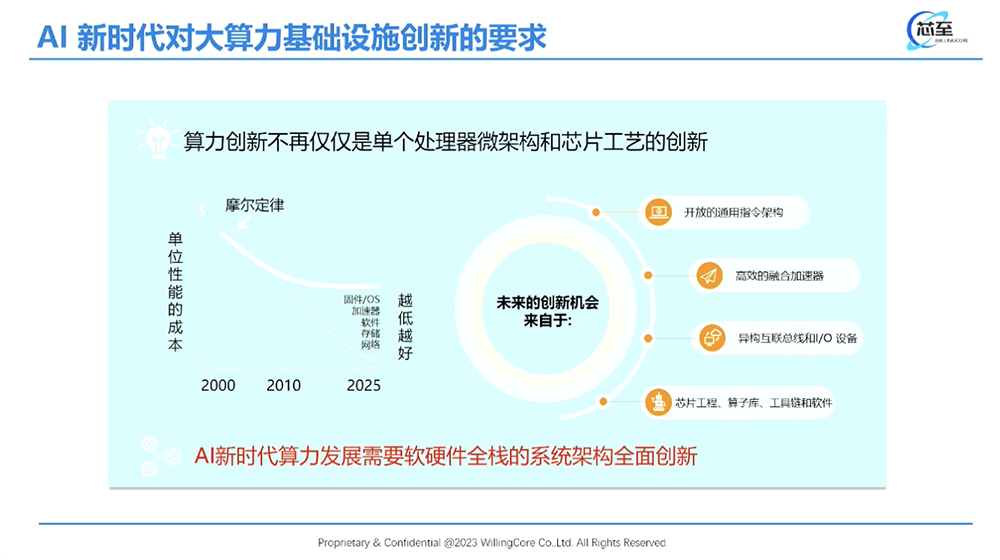

01.AI新時代對算力發展提出新要求:軟硬件全棧的系統架構全面創新

進入AI計算的新時代,怎么催生芯片架構不停地往前推?推向一個什么樣的地方?我們提出了一個“算力統一場”的概念。首先看芯片架構的創新,摩爾定律的一個根本特征就是單位性能的成本在線性下降,但最近幾年,單純憑工藝,到5nm、3nm之后,成本下降并不是線性的。我們怎么樣去延續這個線性的性價比的降低?更多地是要靠軟硬件重構。重構的一個頂層思想其實是來自第一性原理,要把原來的架構不停地分解,再不停地重構。

從芯片架構的角度來看,我們看到了幾個機會:第一個是開放的通用指令架構,上個月(8月份)在北京的RISC-V峰會,各位同行有很多的討論,RISC-V就是開源開放架構的典型代表。第二個是怎樣做一個高效融合的加速器。大模型應用需要底層適應這些模型的算力架構,算力架構怎樣融合在通用指令架構上,這是我們所面臨的機會,也是一個技術難題。另外,現在處理器核越來越多,多Die互聯、異構互聯、存儲的連接越來越復雜,怎樣有一個異構互聯的高效總線,還有高效互聯的I/O設備的一個新架構,是未來AI芯片架構的一個新方向。最后,芯片的晶圓和Die越來越大,功耗越來越大,在提升它的性價比、能效上需要一個非常強大的、可演進的一個芯片工程的支持,以及整個算子庫、工具鏈和軟件的發展。

02.AI大模型推理新機會,與RISC-V架構創新不謀而合

大模型和RISC-V在最近幾年有很好的結合,算法、算力、數據三架馬車要齊步往上推,我們看到,在微架構和模型方面是同步發展的。左邊的圖是大模型在快速發展,云端訓練的大模型有點類似于一個人,首先從0到1,經過九年義務教育,形成完整的世界觀。未來這些大模型要在各行各業去應用,就好比大家上了大學,選定一個專業,進入到一個行業。有句話叫“學好數理化”,數理化就是基礎,未來模型要不停地增加行業知識,那是一個fine-tuning(微調)階段,意味著更多的機會,大模型在各個行業能夠不停部署,產生真正的市場價值。

從右邊的圖可以看到,RISC-V的Scaler部分,有一個通用開源的超標量架構,可以幫助我們打造在處理器主機端的軟硬件棧的基礎。另外基于RISC-V的BSD協議,它有非常廣闊的指令擴展空間。在上面綠色和紫色的部分,我們可以自定義Vector(向量)、Tensor Core(張量核)這些單元,這是RISC-V的指令框架所允許的。然后我們可以在這個擴展指令框架下,去實現各種各樣的微架構,微架構就是芯片架構所具體實現的電路,包括矩陣乘、卷積等電路。RISC-V所帶來的一個很大價值是上游性價比的急劇提升。舉個例子,大家可能不知道對OpenAI的Triton是否熟悉,現在有很多年輕的朋友正在利用Triton這個工具來做AI算子自動化的開發。Triton有全開源的優勢,另外它可以通過自動化的生成工具,來生成特定的一些算子,比如說浮點的卷積或者是矩陣乘。基本上它的效率和手寫的算子庫效率是相當的,比如說一個FP16的矩陣乘,一個Python的代碼可能就20多行,大家可以在網上找到很多例子。它支持像Python這樣的高級語言,可以極大降低通過自定義指令學習類似CUDA這樣編程框架的成本。按照現在Triton的發展,相比CUDA,它在自動化算子生成、內存優化、SM核心的scheduling等方面有很好的效果。

Triton目前是和整個RISC-V的生態圈、全球大的趨勢同步發展,發展速度非常快。另外它也可以避免不兼容的指令,因為RISC-V整個行業在推進,在生態建設上是齊頭并進。我們基于傳統的GPGPU方案會有大量自定義的算子,并且要開發自己的編譯器。作為一個芯片公司,其實我們在軟件的投入上反而會更大,包括在工具鏈、算子庫的開發,很多軟件開發團隊可能高達70%~80%的規模。如果采用開源指令和開源工具鏈這樣的技術路線,首先RISC-V可以復用整個編譯器的開放成果,另外在客戶支持、算子開發這方面,有類似于像Triton,還有未來會發展更多的開源工具,可以自動化地生成第三方算子,極大降低軟件開發的人力成本。

03.一致性總線使通用和異構算力緊密耦合,大幅提升有效算力

算力效率方面,我們提到了“有效算力”概念,跟芯片效率是非常相近的概念。現在我們做芯片架構的時候,在關注單核的算力、主頻、流水線的能力。并且我們還要看在一張晶圓上可以做多少Chiplet的Die,Chiplet集成得越多,算力、核數也會越多越大。但大家可能忽略了一點,就是我們的SoC,把那么多核互聯起來,包括die-to-die的Chiplet互聯,還有CPU和GPU這樣類似于NVLink、CXL這樣的異構互聯,它的效率問題。我們要關注這么幾個指標,包括總線的時延、帶寬、一致性的能力。可能大家對一致性的理解不是特別多,它就好比部門越來越多,雖然團隊的實力和規模越來越大,但是并不代表這么多團隊產生的有效績效能夠越來越強,需要各部門的互聯互通、能夠目標一致。這個一致性也是一樣的,我們有那么多的CPU核、AI核,包括同構、異構的核,怎么保證處理任務的一致性。最后是功耗,它的能效也非常重要。

當前業界在總線方面的發展,包括Die內的Ring/Crossbar總線架構,還包括最近英偉達在Grace芯片里自研開發的Scalable Coherency Fabric,都是在總線上面的一些技術探索。剛才很多同行也介紹了die-to-die(D2D)、Chiplet、并行、UCIe等各種D2D互聯總線,怎么樣提高它的效率,以及我們在一個大的集群里面怎么樣把異構的芯片通過Switch互聯起來,這更多是一個系統上的概念。一致性總線最終的目的是為了通用和異構,就是各種算力能夠有效互聯,來提高它的有效算力。

04.芯片工程新技術突破內存墻瓶頸,極大降低帶寬成本

說完互聯墻,接下來就是大家談論比較多的內存墻。在AI芯片,我們當前的方案更加依賴于HBM這種大帶寬的內存。HBM跟CoWoS相結合,在擴展帶寬的時候,線性擴展帶來成本的極大增長。怎么樣把AI的邏輯Die跟內存Die有更緊密的連接,把帶寬成本降下來?現在我們可以看到,Hybrid Bonding異構鍵合技術在快速發展。基于Hybrid Bonding技術,我們可以實現Wafer-on-Wafer(WoW)的垂直互聯,就像從三樓到四樓可以有上萬部電梯,這樣我們會場這么多人,吞吐率就會非常大。我們芯至科技和合作伙伴一起,現在已經可以做到在兩個Die有70000多個pins互聯,相當于有這么多部電梯互聯互通,容量可以做到6GB,相當于我的AI邏輯Die和內存Die可以實現非常短距的、大帶寬的互聯互通。

由于我們可以不用那么大的die,我們可以極大降低WoW這樣一個內存架構的成本,從計算效率來看,雖然HBM的容量比較大,但實際上在大模型Transformer方面,網絡是分層的。可以看右邊的表格,剛才提到大模型未來進入行業部署更多是微調,它的模型參數并沒有像ChatGPT或者GPT-4、5未來指數級的增長,單層參數量可以放在WoW這樣一個DRAM存儲空間上。在容量夠的情況下,實際上就可以體現WoW這樣一個大帶寬的巨大優勢。

05.圍繞三大方向構建創新架構,打造約10倍性價比優勢的大模型推理芯片

小結一下,在AI架構創新方面,作為芯片架構師,我們還有很多事情可以做:一方面,開放的指令架構。我們可以重新來認識一下RISC-V,它可以做CPU,大家可能熟知的是x86指令、Arm指令,RISC-V就是下一代新生的CPU指令架構。但我們基于RISC-V也可以做SIMT的架構,實現GPGPU的功能。在通過RISC-V做GPGPU的過程中,我們可以最大地復用RISC-V這個開源指令,包括它的開源工具、整個軟件復用度,就可以極大降低在做自定義芯片的情況下,我們要有大量的人力成本。第二,高效的異構互聯,在自研一致性總線方面,我們更多要有一個系統框架,怎么樣把Die內的互聯、D2D Fabric、整個Chip-to-Chip的互聯納入到一個完整的一致性框架下,并且在物理上、在芯片工程上降低時延,提升帶寬,這是我們要發力的重點。第三,新型的芯片工程,在內存墻方面,我們怎么樣把AI Die通過WoW、Hybrid Bonding這樣的技術,把帶寬做上去,未來是能夠替代HBM、CoWoS封裝等高成本方式的最佳途徑。所以我們團隊現在在考慮,在當前的大模型推理芯片架構上,在軟硬件結合還有芯片工程上的創新,來打造具有10倍性價比以上的創新芯片。

06.結語:重構計算體系結構,打造算力統一場,發展軟件大生態

中長期愿景,算力統一場。首先可以看到中間這個圖,在整個RISC-V指令規劃基礎下,我們在這個圓圈的內部可以做很多事情。

我們的DSA和通用架構,實際上是一個循環,在80年代的時候,當時一個叫牧村的日本人提出的“牧村定律”,就是從專用到通用這個循環的規律。RISC-V的整體指令架構是統一或同構的,但我們可以在微架構做很多事情,包括SIMT、DSP、DSA的核心等,來發揮RISC-V在整個開放指令上的優勢。另外一點,開源工具鏈,就像我剛才給大家介紹的OpenAI所做的Triton的例子,大家可以多去看看,Triton在整個社區非常活躍。未來會有更多像Triton這樣的開源工具發展,結合RISC-V微觀指令的發展,在整個指令、自定義算子、編譯器方面,有很大的性價比提升。從微架構異構和指令集同構、開源工具鏈、在SoC層面的一致性總線還有芯片工程方面,我們有機會在未來打造一個軟硬件同構的新生態。這個新生態更加有利于在國內形成一個更大的、自主可控的軟件生態,并且在芯片架構領域更加符合計算架構本身原生態的架構,有助于在計算領域幫助我國在計算體系方面做到換道超車。大家知道當前的CPU、GPU的計算架構和生態是建立和發展主要在國外,國外特別是硅谷有很多行業前輩奠定了在傳統計算架構上面的基礎。在未來算力統一場的新方向,我們可以做很多自主可控的架構創新。在AI新時代新機遇的引領下,希望我們團隊和整個芯片行業同仁一起,能夠把算力同一場的愿景不斷地做好、做遠,共同實現計算新生態。謝謝大家!以上是尹文演講內容的完整整理。

*博客內容為網友個人發布,僅代表博主個人觀點,如有侵權請聯系工作人員刪除。