天科合達談八英寸SiC

來源:內容來自來源:人工晶體學報,作者:婁艷芳、劉春俊等 單位:北京天科合達半導體股份有限公司,謝謝。

引 言

2.實 驗

2.1

晶體生長和襯底制備

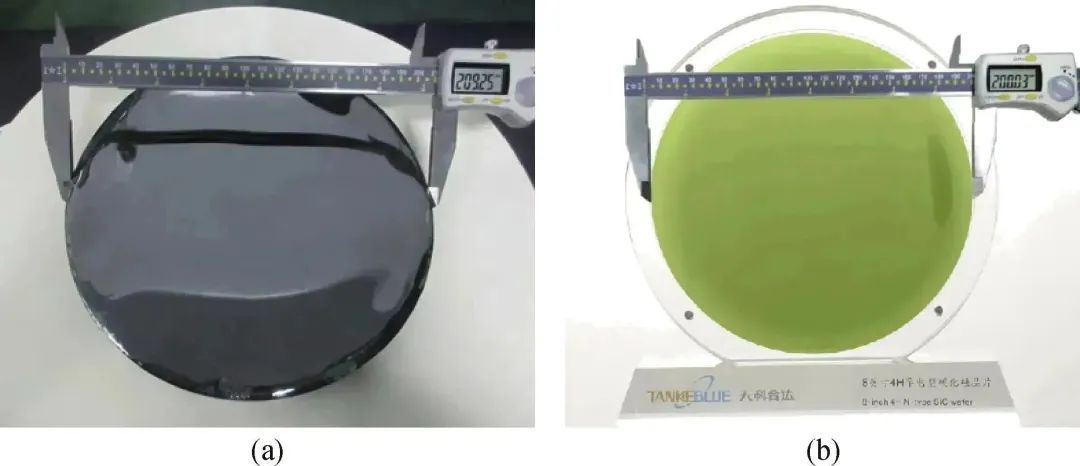

本實驗通過以自主研發(fā)的由c軸偏向<11-20>方向4°的6英寸4H-SiC襯底作為籽晶和擴徑生長的起始點,采用物理氣相傳輸(physical vapor transport, PVT)法進行擴徑生長獲得直徑放大的SiC單晶。將放大的晶體進行切、磨、拋得到放大的新籽晶,通過多次迭代實現(xiàn)直徑放大到200 mm以上,從而獲得8英寸SiC晶體。生長過程中選擇籽晶的碳面作為生長表面,原料端溫度維持在2300 ℃左右,籽晶端的溫度控制在2100 ℃左右,壓力控制在4000 Pa以下,保持一定比例的氬氣和氮氣流動氣氛調控n型摻雜,從而實現(xiàn)導電型4H-SiC單晶的穩(wěn)定生長。生長完成后的晶體進行滾圓、磨平面得到標準直徑的8英寸晶柱,以多線切割的方式進行切片,而后將切片進行研磨、拋光、清洗等一系列流程,制備出標準尺寸的8英寸導電型4H-SiC襯底。2.2

性能表征

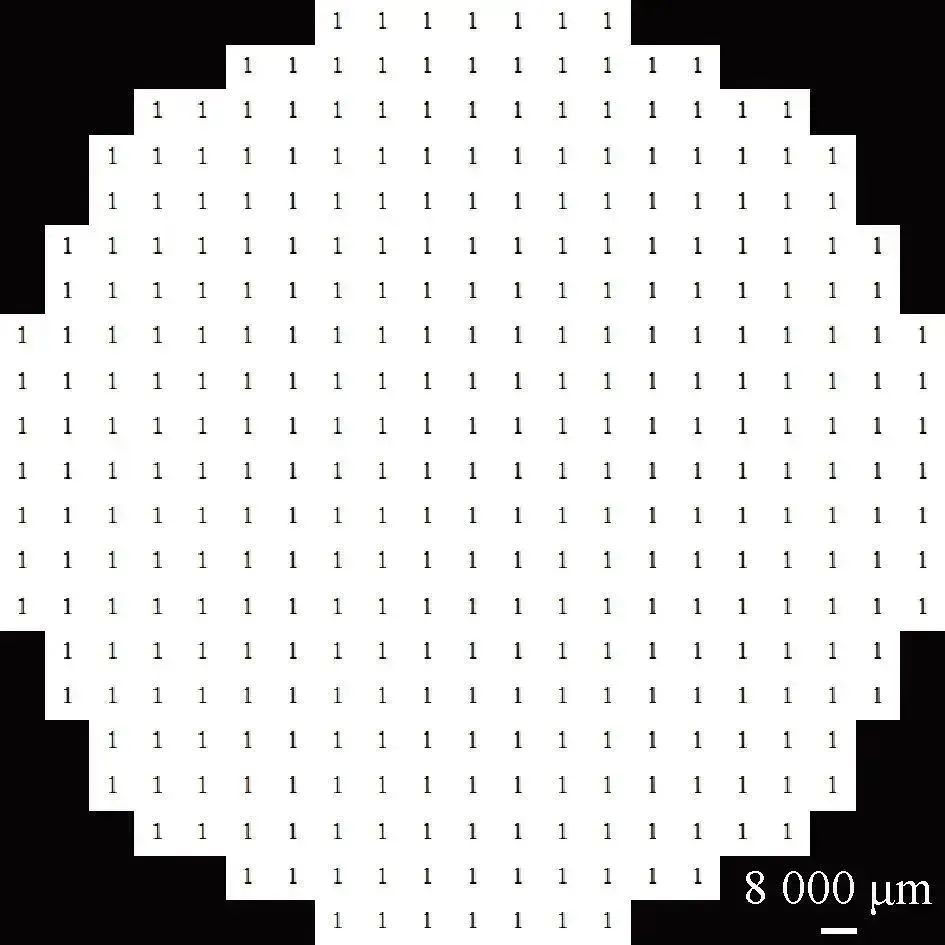

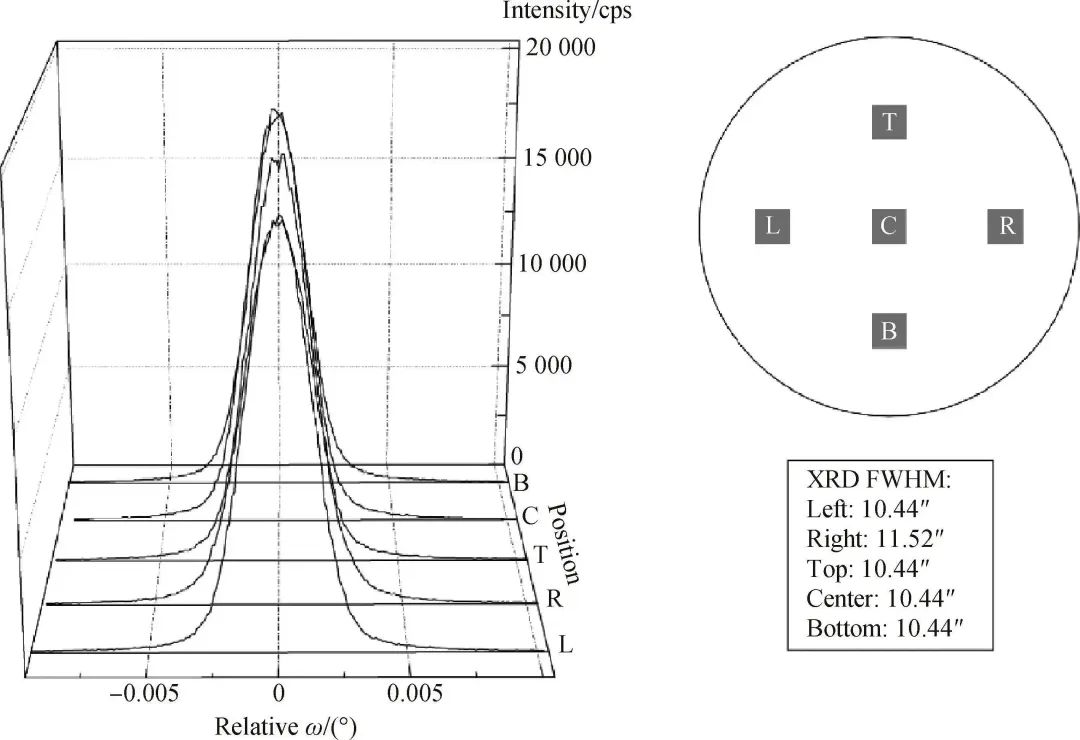

使用LabRamHR800型拉曼測試儀對8英寸4H-N-SiC襯底進行拉曼光譜檢測,激發(fā)光源為532 nm,光斑大小為直徑721 nm,共檢測357點位,對襯底的晶型進行表征;使用Panalytical-X’Pert3 MRD XL型高分辨X射線衍射儀進行結晶質量檢測,采用單色源Cu Kα射線(λ=0.15406 nm),測試范圍為±0.02°,步長0.0001°, 積分時間0.1 s,檢測襯底上、下、左、中、右半徑中點處共5點位(004)衍射面的搖擺曲線,用以表征襯底的結晶質量;使用光學顯微鏡檢測襯底的微管數(shù)量和分布位置,并計算出微管密度;使用非接觸式電阻儀,參照SEMI-MF673中的方法Ⅱ[7],即非接觸渦流法測量襯底55點位的電阻率;使用應力檢測儀對8英寸襯底的應力進行表征,該設備利用光在不同應力條件下傳播會產生相位差這一特性,通過觀察疊加偏振的光明暗來定性辨別應力大小和分布;使用Tropel? FlatMaster 200對8英寸襯底的面型進行測量,該設備利用分析樣品與設備參考平面反射光形成的干涉條紋來識別樣品的面型和厚度變化;使用540 ℃熔融KOH對襯底進行20 min刻蝕,并采用全自動位錯掃描儀對其位錯分布及密度進行掃描和統(tǒng)計。3.結果與討論

圖1 天科合達8英寸SiC晶錠和晶片。(a)直徑達到209 mm的SiC晶錠;(b)標準8英寸SiC晶片

拉曼光譜對晶片357點位的測試結果如圖2所示。各測試點位均出現(xiàn)形貌相似的拉曼峰,且與聲子模以及簡約波矢和對稱性為204 cm-1(FTA,x=0.5,E2)的拉曼峰偏差不大于0.65 cm-1。與此同時,結果中未測得6H晶型對應的FTA模(150 cm-1),以及15R晶型對應的FTA模(174 cm-1)等高強度簡約波矢模[8]。由此可得8英寸SiC晶片的4H晶型占比為100%。

圖2 8英寸4H-SiC晶片拉曼光譜掃描圖(1為4H-SiC,2為6H-SiC,3為15R-SiC)

高分辨率X射線搖擺曲線測試結果如圖3所示,測試點位為襯底中心和上、下、左、右半徑的中心位置共5點。從圖中可以看出,各測試點位的(004)衍射峰均為單一峰,其對應的半峰全寬分布在10.44″至11.52″之間,表明8英寸4H-SiC襯底結晶質量良好,不存在多晶、小角晶界等影響結晶質量的缺陷。

圖3 8英寸SiC晶片(004)晶面高分辨X射線衍射圖譜

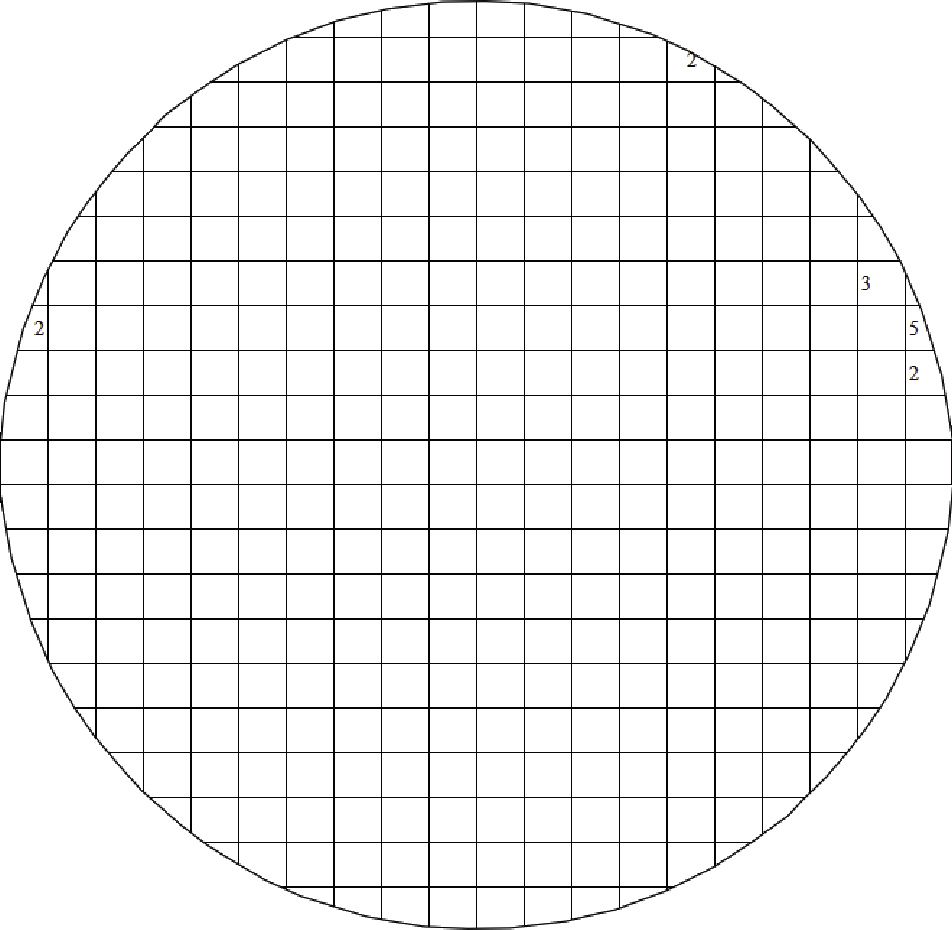

使用光學顯微鏡對8英寸襯底的微管密度進行全自動掃描,去除邊緣3 mm區(qū)域的微管進行統(tǒng)計后得出,該8英寸襯底的微管密度為0.04 cm-2。整片中共發(fā)現(xiàn)微管14個,且均分布于邊緣,如圖4所示。

圖4 8英寸SiC晶片微管分布

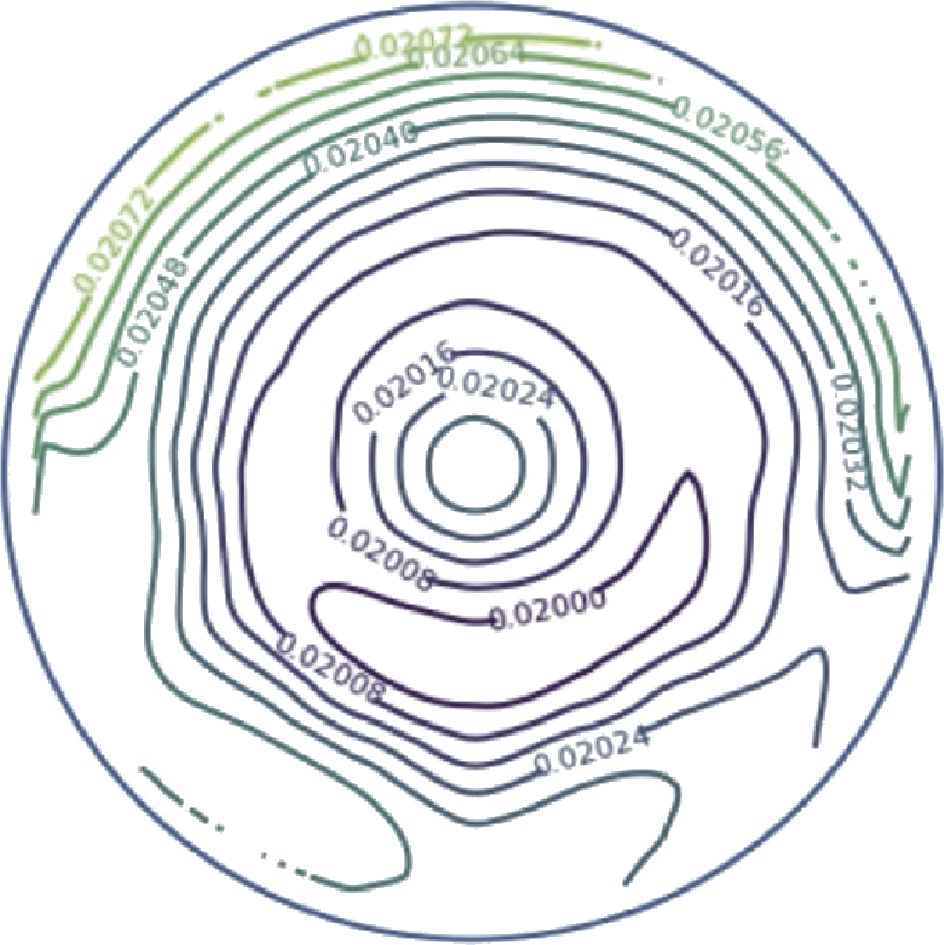

采用非接觸式渦流法測試8英寸SiC襯底電阻率,結果如圖5所示。結果顯示,8英寸襯底的平均電阻率為0.0203 Ω·cm,最大值為0.0208 Ω·cm,最小值為0.0199 Ω·cm,相對標準偏差為1.11%。

圖5 8英寸SiC晶片電阻率測試結果

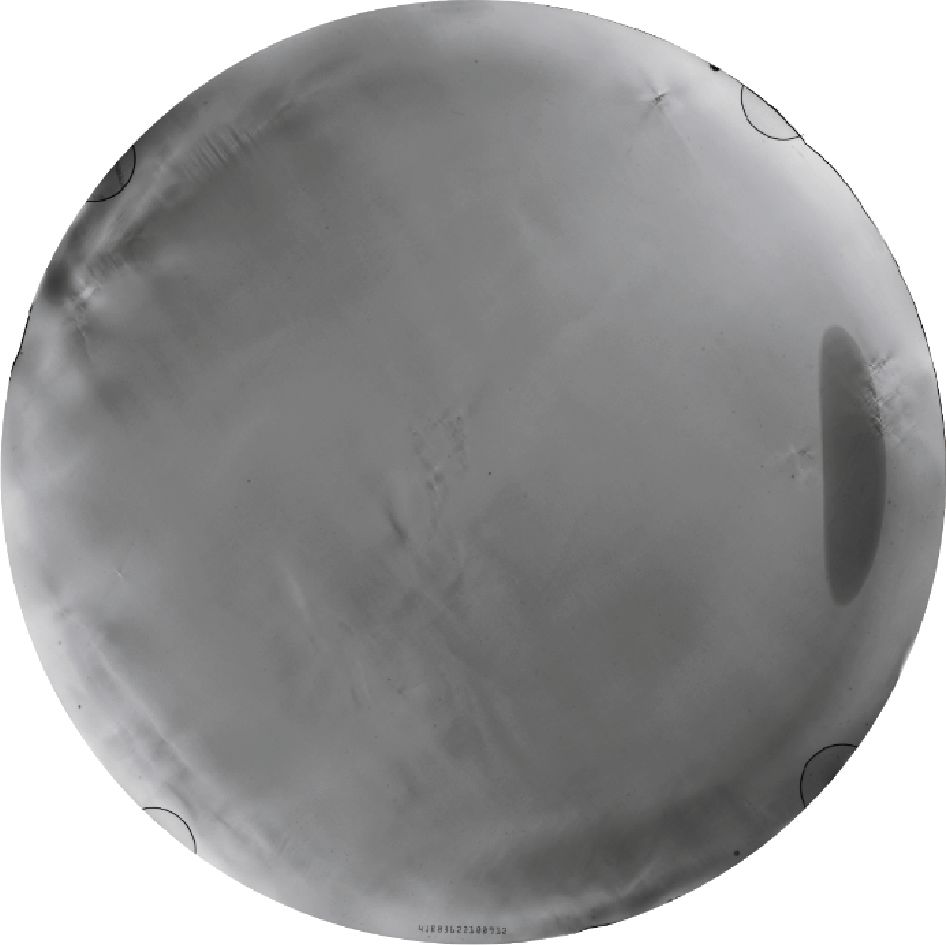

采用偏振光應力儀檢測的8英寸襯底應力分布,如圖6所示。一般地,測試結果中明暗波動較大的區(qū)域應力較大[9]。該8英寸SiC襯底整體應力分布均勻,除在小面位置外側以及襯底邊緣位置存在低強度應力區(qū)域外,大部分區(qū)域未見明顯的應力集中區(qū)域,表明晶體的結晶質量良好。

圖6 8英寸SiC晶片偏振光應力測試結果

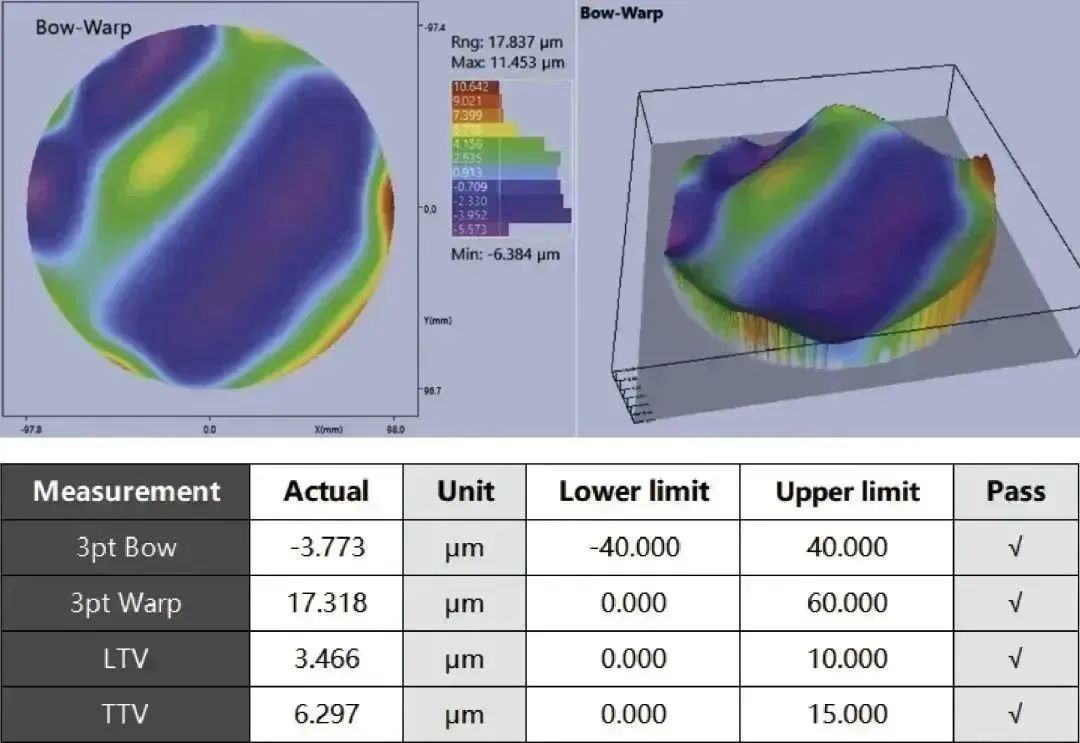

使用FM200測試的晶片面型結果如圖7所示。通過測量得出該8英寸晶片的3點彎曲度(Bow)為-3.773 μm,3點翹曲度(Warp)為17.318 μm。

圖7 8英寸SiC晶片平整度測試結果

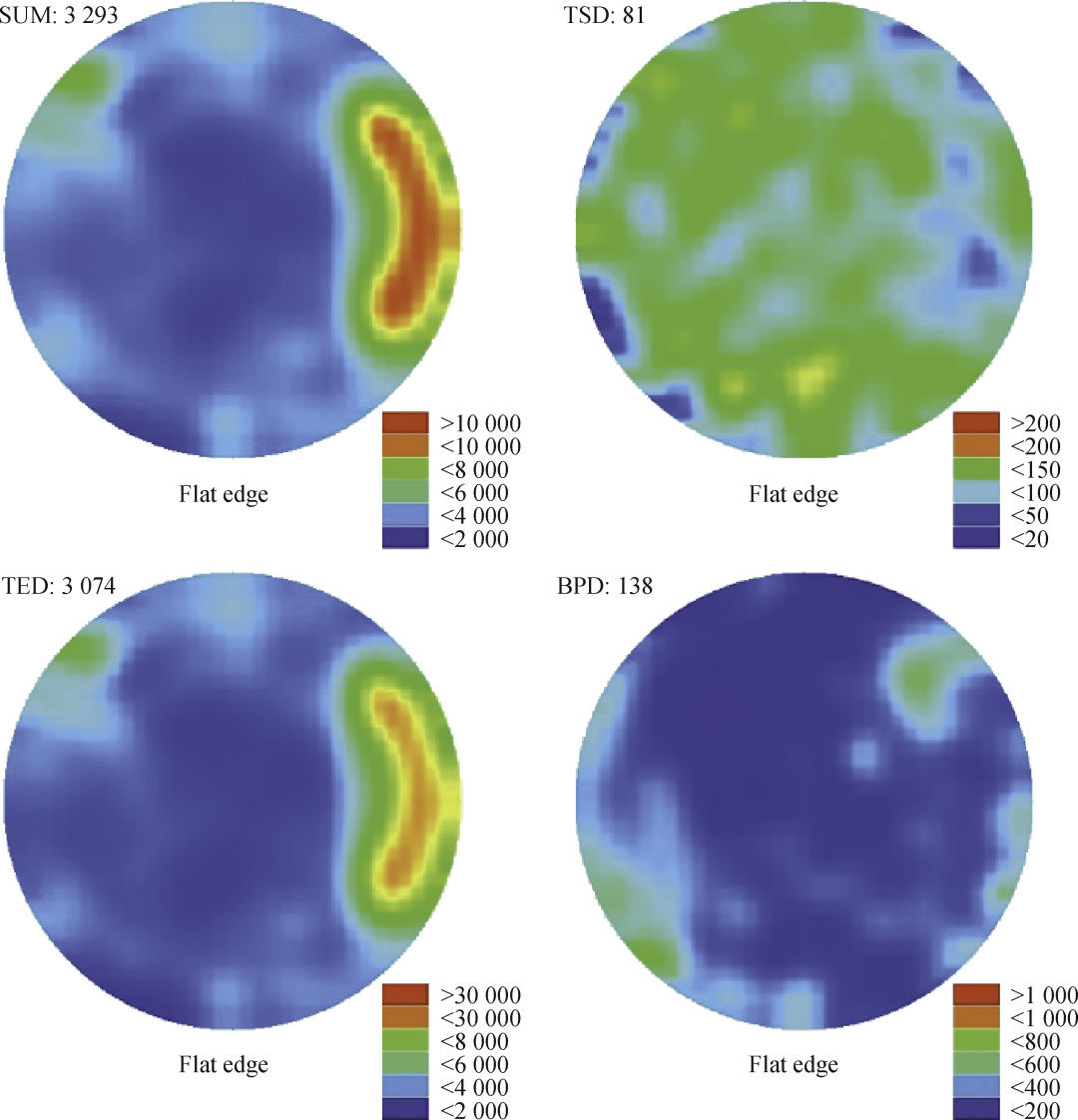

通過熔融KOH刻蝕,SiC襯底硅面表面的位錯位置被擇優(yōu)腐蝕放大,即位錯腐蝕坑。使用自動位錯檢測儀對腐蝕坑的形貌進行識別和分類,并統(tǒng)計出位錯在襯底上的分布和位錯密度。結果顯示,該8英寸襯底的位錯腐蝕坑密度(etch pit density, EPD)為3293 cm-2,其中螺型位錯(threading screw dislocation, TSD)密度為81 cm-2,刃型位錯(threading edge dislocation, TED)密度為3074 cm-2,基平面位錯(basal plane dislocation, BPD)密度僅為138 cm-2。各類型位錯的分布如圖8所示。由于小面區(qū)域的生長習性與其他區(qū)域不同,導致位錯密度在此位置明顯高于其他區(qū)域,符合理論預期。

圖8 8英寸SiC晶片位錯分布圖

綜合上述結果,該SiC襯底的各項指標與當前6英寸SiC襯底的行業(yè)標準[10-11]相當,可滿足后續(xù)8英寸外延、器件等加工要求。4.結 論

來源:人工晶體學報 作者:婁艷芳、劉春俊等 單位:北京天科合達半導體股份有限公司

*博客內容為網(wǎng)友個人發(fā)布,僅代表博主個人觀點,如有侵權請聯(lián)系工作人員刪除。

電機保護器相關文章:電機保護器原理 三維掃描儀相關文章:三維掃描儀原理 熱保護器相關文章:熱保護器原理