- 在FPGA系統中,實現對外部A/D數據采集電路的控制接口邏輯,由于其邏輯功能不是很復雜,因此可采用自定義的方式。采用這種方法進行設計有兩種途徑。①從軟件上去實現。這種方案將NIOS處理器作為一個主控制器,通過編寫程序來控制數據轉換電路。由于NIOS處理器的工作頻率相對于外部設備來說要高出許多,故此種方法會造成CPU資源極大的浪費;②用FPGA 的邏輯資源來實現A/D采集電路的控制邏輯。FPGA有著豐富的邏輯資源和接口資源,在其中實現并行的數據采集很少會受到硬件資源的限制,在功能上,設計的接口控制邏輯相當于

- 關鍵字:

模擬技術 電源技術 0708_A 雜志_高校園地 NIOS-II 數據采集 模擬IC 電源

- 摘 要:本設計應用Altera 公司的Cyclone II系列的FPGA(現場可編程門陣列)實現了對步進電機正弦波可變細分控制,并在FPGA中進行了具體驗證和實現。該方案綜合運用了電流跟蹤型SPWM技術、PI調節、片上可編程系統SOPC技術、EDA技術等。步進電機控制系統用FPGA實現了Nios II軟核處理器與硬件邏輯電路集于一體,發揮了處理器的靈活性和數字邏輯電路高速性,有效地解決了步距角的高細分問題,細分數最高達4096,而且細分數可自動調節。實驗

- 關鍵字:

嵌入式系統 單片機 步進電機驅動器 Nios II 嵌入式

- 摘 要:針對傳統Otsu局部遞歸分割方法很難實時實現的局限性,提出了一種適合現場可編程門陣列(FPGA)中Nios II軟核處理器實現的快速Otsu局部遞歸分割算法,該算法的思路是把一次Otsu分割得到的目標區域作為新的圖像再進行一次Otsu分割,得到的結果作為最終分割閾值.利用并行Nios II和VHDL實現的硬件加速邏輯協同設計保證算法的實時實現。實驗結果表明,在不同的背景下,利用本文設計能夠實時穩定地對目標分割提取,具有較好的魯棒性。 關鍵字:FPGA&nb

- 關鍵字:

嵌入式系統 單片機 FPGA Nios II 0tsu分割 局部遞歸 嵌入式

- μC/OS-II下通用驅動框架的設計與實現,在μC/OS-II下,設計了一個通用的設備管理模型,稱為通用驅動框架,通過該驅動框架,可以實現對硬件設備的統一、一致的管理,同時,也為上層應用程序提供了統一、一致的設備訪問接口,并在以ARM7TDMI-S為核心的LPC2210微控制器開發板上給出了一例實現。

- 關鍵字:

設計 實現 框架 驅動 通用 C/OS-II

- Xilinx Virtex-5 SXT FPGA 平臺提供了獨特的單芯片解決方案,充分利用大規模并行計算達到超高性能,同時將功耗降到最低。

- 關鍵字:

Virtex SXT DSP 性能

- 二十多年來,FPGA 為世人提供了最靈活、適應性極強、快速的設計環境。早期的 DSP 設計人員發現,可將一種可再編程的門海用于數字信號處理。如果把內置到 FPGA 架構中的乘法器、加法器和累加單元結合起來,就可以利用大規模并行計算實現有效的濾波器算法。

在未加工頻率性能方面的損失,通過并行計算得到了彌補,而且得遠大于失,可謂“失之東隅,收之桑榆”;由此獲得的 DSP 帶寬完全可與替代方案媲美。隨著時間的推移,乘法器和加法器的實施越來越高效。1998 年,Xilinx 順理成章推出了第一個集成于

- 關鍵字:

嵌入式系統 單片機 DSP Virtex-5 嵌入式

- 在本文中,我將分析功耗降低所帶來的好處。還將介紹 Virtex-5 器件中所使用的多種技術和結構上的革新,它們能提供功耗最低的解決方案,并且不會在性能上有任何折扣。

- 關鍵字:

Virtex FPGA 低功耗

- 隨著嵌入式系統應用的日益廣泛,如何實現嵌入式系統的低功耗開發已經成為嵌入式應用發展的關鍵技術之一,是近幾年來人們在嵌入式系統的設計中普遍關注的難點與熱點。嵌入式系統正被廣泛應用于移動性較強的產品中去,而這些產品不是一直有充足的電源供應,往往需要電池來供電,因此,設計人員需要從每一個細節來考慮降低系統的功率消耗,從各個方面去實現降低系統的功耗。同時功耗對終端設備的成本及體積大小有顯著影響。

本文結合FM電臺手持式測試儀這一實例,從系統硬件設計、系統軟件設計、利用內核擴展接口和產品應用特點這四個方

- 關鍵字:

嵌入式系統 單片機 μC/OS-II 低功耗開發 嵌入式

- 基于LPC2214和uC/OS-II 的音頻處理方案,對LPC2214和uC/OS-II相結合的嵌入式平臺的性能進行大概的分析;介紹音頻編解碼芯片VSl003的特點及其讀寫控制協議的實現方式;著重介紹如何采用VSl003為基于LPC2214和uC/OS-II的嵌入式平臺提供音頻處理接口。

- 關鍵字:

處理 方案 音頻 OS-II LPC2214 uC 基于

- 賽靈思公司日前隆重宣布,其屢獲殊榮的65nm Virtex-5 FPGA系列兩款器件LX50 和 LX50T最先實現量產。自2006年5月15日推出65nm Virtex-5 FPGA平臺以來,賽靈思目前已向市場發售了三款平臺(LX、LXT和SXT)的13種器件,它們為客戶提供了無需任何折衷的業界最高的性能、最低的功耗, 并擁有業界唯一內建的PCI Express®™ 端點和千兆以太網模塊,以及業界最高的DSP性能。

賽靈思公司高級產品部執行副總裁Iain Morris 表示

- 關鍵字:

65nm FPGA VIRTEX-5 單片機 嵌入式系統 賽靈思

- 1 基于 LPC2214和uC/OS-II的嵌入式平臺目前流行的ARM芯片內核有ARM7TDMI、ARM720T、ARM9TDMI、ARM992T、ARM940T、ARM946T、ARM966T和ARM10TDMI等,Philips LPC2214是基于ARM7TDMI-S的高性能32位RISC微控制器,它集成了Thumb擴展指令集,256KB可在系統中編程的片內Flash和可在應用中編程的16位KB RAM,向量中斷控制器,外部總線控制器,2個UART,I2C串行接口,2個SPI串行接口,2個定時器(7

- 關鍵字:

LPC2214 uC/OS-II 單片機 嵌入式系統 音頻處理

- 賽靈思公司宣布日立國際電氣(Hitachi Kokusai Electric)公司生產的KP系列工業相機選用了賽靈思公司的65nm Virtex™-5 LX FPGA器件。越來越多的工業網絡生產商一樣,日立國際電氣意識到賽靈思公司高性能Virtex-5 FPGA的密度和功耗優勢能夠為其提供終極的設計靈活性和更快的產品上市時間。

日立國際電氣公司最新的高分辨率快幀速率KP系列(七種類型,14個型號)產品圖像質量好、效率高并且速度快。由于其尺寸小,易于安裝和使用,因此該系列產品適用于廣

- 關鍵字:

KP系列 VIRTEX-5 單片機 工業相機 嵌入式系統 日立 賽靈思

- 在FPGA系統設計中,要達到性能最大化需要平衡具有混合性能效率的元器件,包括邏輯構造(fabric)、片上存儲器、DSP和I/O帶寬。在本文中,我將向你解釋怎樣能在追求更高系統級性能的過程中受益于Xilinx® 的Virtex™-5 FPGA構建模塊,特別是新的ExpressFabric™技術。以針對邏輯和算術功能的量化預期性能改進為例,我將探究ExpressFabric架構的主要功能。基于實際客戶設計的基準將說明Virtex-5ExpressFabric技術性能平均比前一

- 關鍵字:

FPGA Virtex-5 單片機 嵌入式系統

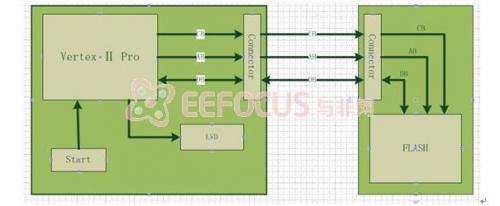

virtex-ii介紹

您好,目前還沒有人創建詞條virtex-ii!

歡迎您創建該詞條,闡述對virtex-ii的理解,并與今后在此搜索virtex-ii的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473