EEPW首頁(yè) >>

主題列表 >>

risc-v 架構(gòu)

risc-v 架構(gòu) 文章 最新資訊

架構(gòu)與ISA:移動(dòng)處理器的真正關(guān)鍵

- 我最近參加了the Linley Tech Mobile Conference (Linley Tech移動(dòng)技術(shù)研討會(huì)),這是每年在硅谷連續(xù)舉辦兩天的技術(shù)研討會(huì),聚焦于移動(dòng)處理議題。參與的廠商包括Synopsys、英特爾、GLOBALFOUNDRIES、高通(容我補(bǔ)充,

- 關(guān)鍵字: 架構(gòu) ISA 移動(dòng)處理器

ARM 架構(gòu)/特性(處理器)全解

- ARM 架構(gòu)是構(gòu)建每個(gè) ARM 處理器的基礎(chǔ)。ARM 架構(gòu)隨著時(shí)間的推移不斷發(fā)展,其中包含的架構(gòu)功能可滿足不斷增長(zhǎng)的新功能、高性能需求以及新興市場(chǎng)的需

- 關(guān)鍵字: ARM 架構(gòu) 特性 處理器

馮·諾依曼架構(gòu)

- 馮·諾依曼結(jié)構(gòu)也稱(chēng)普林斯頓結(jié)構(gòu),是一種將程序指令存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器合并在一起的存儲(chǔ)器結(jié)構(gòu)。程序指令存儲(chǔ)地址和數(shù)據(jù)存儲(chǔ)地址指向同一個(gè)存儲(chǔ)器的不同物理位置,因此程序指令和數(shù)據(jù)的寬度相同,如英特爾公司的8086中央處理器的程序指令和數(shù)據(jù)都是16位寬。架構(gòu)圖如下:在典型情況下,完成一條指令需要3個(gè)步驟,即:取指令、指令譯碼和執(zhí)行指令。舉一個(gè)最簡(jiǎn)單的對(duì)存儲(chǔ)器進(jìn)行讀寫(xiě)操作的指令,指令1至指令3均為存、取數(shù)指令,對(duì)馮?諾曼結(jié)構(gòu)處理器,由于取指令和存取數(shù)據(jù)要從同一個(gè)存儲(chǔ)空間存取,經(jīng)由同一總線傳輸,因而它們無(wú)法重疊執(zhí)行,只

- 關(guān)鍵字: 架構(gòu) 馮諾依曼

哈佛架構(gòu)

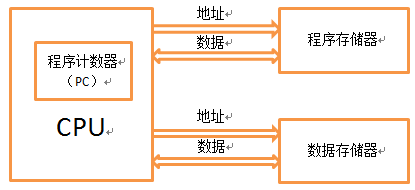

- 哈佛結(jié)構(gòu)是一種存儲(chǔ)器結(jié)構(gòu)。使用哈佛結(jié)構(gòu)的處理器有:AVR、ARM9、ARM10、ARM11等。哈佛結(jié)構(gòu)是一種將程序指令存儲(chǔ)和數(shù)據(jù)存儲(chǔ)分開(kāi)的存儲(chǔ)器結(jié)構(gòu)。是一種并行體系結(jié)構(gòu),數(shù)字信號(hào)處理一般需要較大的運(yùn)算和較高的運(yùn)算速度,為了提高數(shù)據(jù)吞吐量,在數(shù)字信號(hào)處理器中大多采用哈佛結(jié)構(gòu)。哈佛結(jié)構(gòu)的計(jì)算機(jī)由CPU、程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器組成,程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器采用不同的總線, 特點(diǎn):1、將程序和數(shù)據(jù)存儲(chǔ)在不同的存儲(chǔ)空間中,即程序存儲(chǔ)器和數(shù)據(jù)存儲(chǔ)器是兩個(gè)獨(dú)立的存儲(chǔ)器,每個(gè)存儲(chǔ)器獨(dú)立編址、獨(dú)立訪問(wèn)。

- 關(guān)鍵字: 架構(gòu) 哈佛架構(gòu)

SPARC架構(gòu)與X86架構(gòu)介紹

- SPARC(Scalable Processor ARChitecture,可擴(kuò)展處理器架構(gòu))是國(guó)際上流行的RISC處理器體系架構(gòu)之一,SPARC如今已發(fā)展成為一個(gè)開(kāi)放的標(biāo)準(zhǔn),任何機(jī)構(gòu)或個(gè)人均可研究或開(kāi)發(fā)基于SPARC架構(gòu)的產(chǎn)品,而無(wú)需交納版權(quán)費(fèi)。SPARC 處理器架構(gòu)具備精簡(jiǎn)指令集(RISC)、支持32 位/64 位指令精度,架構(gòu)運(yùn)行穩(wěn)定、可擴(kuò)展性?xún)?yōu)良、體系標(biāo)準(zhǔn)開(kāi)放等特點(diǎn)。SPARC因此得以迅速發(fā)展壯大,在現(xiàn)在已經(jīng)有大約3萬(wàn)多個(gè)成功的應(yīng)用案例。SPARC

- 關(guān)鍵字: 架構(gòu) SPARC X86

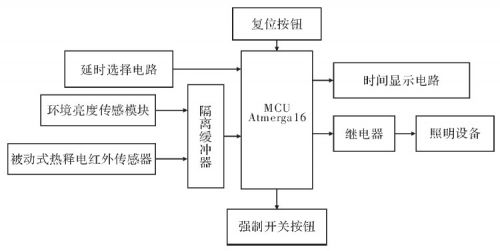

基于Atmega16的室內(nèi)照明系統(tǒng)設(shè)計(jì)

- 照明是室內(nèi)環(huán)境設(shè)計(jì)的重要組成部分,光照的作用,對(duì)人的視覺(jué)功能尤為重要。而長(zhǎng)期以來(lái),將自然光與室內(nèi)智能照明系統(tǒng)相結(jié)合的方式一直被設(shè)計(jì)者忽略,大部分的室內(nèi)場(chǎng)所仍沿用單一的傳統(tǒng)照明方式,在一些公用場(chǎng)所的照明設(shè)備長(zhǎng)時(shí)間打開(kāi),不僅導(dǎo)致能源浪費(fèi),而且加速了設(shè)備老化。 1 系統(tǒng)結(jié)構(gòu)和工作原理 1. 1 系統(tǒng)結(jié)構(gòu) 室內(nèi)照明控制系統(tǒng)的設(shè)計(jì)主要采用Atmega16 單片機(jī)作為MCU 控制器,與LED 顯示技術(shù)、光感技術(shù)、按鍵采集與處理技術(shù)、紅外線傳感技術(shù)、延時(shí)技術(shù)等技術(shù)相結(jié)合,然后實(shí)現(xiàn)室內(nèi)照明設(shè)備的智能

- 關(guān)鍵字: Atmega16 RISC

零基礎(chǔ)學(xué)FPGA(十四)第一片IC——精簡(jiǎn)指令集RISC_CPU設(shè)計(jì)精講

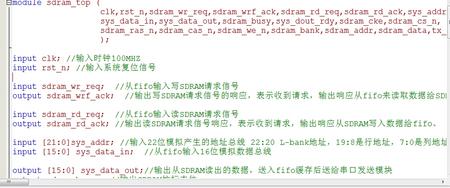

- 不得不說(shuō),SDRAM的設(shè)計(jì)是我接觸FPGA以來(lái)調(diào)試最困難的一次設(shè)計(jì),早在一個(gè)多月以前,我就開(kāi)始著手想做一個(gè)SDRAM方面的教程,受特權(quán)同學(xué)影響,開(kāi)始學(xué)習(xí)《高手進(jìn)階,終極內(nèi)存技術(shù)指南》這篇論文,大家都知道這篇文章是學(xué)習(xí)內(nèi)存入門(mén)的必讀文章,小墨同學(xué)花了一些時(shí)間在這上面,說(shuō)實(shí)話看懂這篇文章是沒(méi)什么問(wèn)題的,文件講的比較直白,通俗易懂,很容易入手。當(dāng)了解了SDRAM工作方式之后,我便開(kāi)始寫(xiě)代碼,從特權(quán)同學(xué)的那篇經(jīng)典教程里面,我認(rèn)真研讀代碼的來(lái)龍去脈,終于搞懂了特權(quán)同學(xué)的設(shè)計(jì)思想,并花了一些時(shí)間將代碼自己敲一遍,

- 關(guān)鍵字: FPGA RISC

基于Microblaze的經(jīng)典設(shè)計(jì)匯總,提供軟硬件架構(gòu)、流程、算法

- Microblaze嵌入式軟核是一個(gè)被Xilinx公司優(yōu)化過(guò)的可以嵌入在FPGA中的RISC處理器軟核,具有運(yùn)行速度快、占用資源少、可配置性強(qiáng)等優(yōu)點(diǎn),廣泛應(yīng)用于通信、軍事、高端消費(fèi)市場(chǎng)等領(lǐng)域。支持CoreConnect總線的標(biāo)準(zhǔn)外設(shè)集合。Microblaze處理器運(yùn)行在150MHz時(shí)鐘下,可提供125 D-MIPS的性能,非常適合設(shè)計(jì)針對(duì)網(wǎng)絡(luò)、電信、數(shù)據(jù)通信和消費(fèi)市場(chǎng)的復(fù)雜嵌入式系統(tǒng)。本文介紹基于Microblaze的設(shè)計(jì)實(shí)例,供大家參考。 雙Microblaze軟核處理器的SOPC系統(tǒng)設(shè)計(jì)

- 關(guān)鍵字: RISC Xilinx GPIO

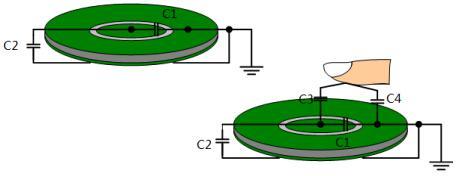

可充電觸屏遙控模塊設(shè)計(jì)

- 摘要 本文介紹了使用MSP430作為主處理器實(shí)現(xiàn)可充電的觸屏遙控模塊,該設(shè)計(jì)方案支持紅外(IR)信號(hào)傳輸,且可擴(kuò)展RF和NFC無(wú)線傳輸方式;用戶(hù)輸入采用觸摸按鍵實(shí)現(xiàn),設(shè)計(jì)簡(jiǎn)潔美觀;系統(tǒng)可由電池供電,且自帶可充電模塊,可由USB或者直流電源適配器充電。TI的430系列MCU產(chǎn)品功耗低,可為便攜式電子設(shè)備提供更長(zhǎng)的使用壽命;其內(nèi)嵌LCD驅(qū)動(dòng)器,可以方便實(shí)時(shí)顯示監(jiān)測(cè)數(shù)據(jù);其支持多種觸摸按鍵實(shí)現(xiàn)方式,設(shè)計(jì)簡(jiǎn)便靈活。 簡(jiǎn)介 遙控設(shè)備在日常生活中非常易見(jiàn),家電遙控器、玩具遙控器等方便了用戶(hù)對(duì)設(shè)備

- 關(guān)鍵字: MSP430 RISC SoC

risc-v 架構(gòu)介紹

您好,目前還沒(méi)有人創(chuàng)建詞條risc-v 架構(gòu)!

歡迎您創(chuàng)建該詞條,闡述對(duì)risc-v 架構(gòu)的理解,并與今后在此搜索risc-v 架構(gòu)的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)risc-v 架構(gòu)的理解,并與今后在此搜索risc-v 架構(gòu)的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司