pll 文章 最新資訊

Silicon Labs推出業(yè)界最低抖動的時鐘系列產(chǎn)品

- 高性能模擬與混合信號IC領(lǐng)導(dǎo)廠商Silicon Labs(芯科實驗室有限公司)今日宣布針對高速網(wǎng)絡(luò)、通信和數(shù)據(jù)中心等當今互聯(lián)網(wǎng)基礎(chǔ)設(shè)施的根基,推出業(yè)界最高頻率靈活性和領(lǐng)先抖動性能的時鐘解決方案。Silicon Labs的新一代Si534x“片上時鐘樹“系列產(chǎn)品包括高性能時鐘發(fā)生器和高集成度Multi-PLL抖動衰減器。這些單芯片、超低抖動時鐘芯片整合了時鐘合成與抖動衰減功能,設(shè)計旨在減少光傳輸網(wǎng)絡(luò)、無線基礎(chǔ)設(shè)施、寬帶接入/匯聚、電信級以太網(wǎng)、測試和測量以及企業(yè)和數(shù)據(jù)中心設(shè)備(包

- 關(guān)鍵字: Silicon Labs Multi-PLL 時鐘

探討如何為定時應(yīng)用選擇合適的PLL振蕩器

- 十幾年前,頻率控制行業(yè)推出了基于鎖相環(huán)(PLL)的振蕩器,這是一項開拓性創(chuàng)新技術(shù),采用了傳統(tǒng)晶體振蕩器(XO)所沒有的多項特性。憑借內(nèi)部時鐘合成器IC技術(shù),基于PLL的XO可編程來支持更寬廣的頻率范圍。這一突破消除了為在特定頻率實現(xiàn)共振而切割和加工石英所需的材料加工工藝步驟。這一創(chuàng)新也使得對基于PLL的XO進行頻率編程成為可能并且實現(xiàn)極短交貨周期。 鑒于傳統(tǒng)振蕩器交貨周期可能接近14周或更長,許多硬件設(shè)計人員渴望利用可編程振蕩器獲得顯著的交貨周期優(yōu)勢。不幸的是,嚴重的問題發(fā)生了。一些已經(jīng)從傳統(tǒng)X

- 關(guān)鍵字: 振蕩器 PLL SoC

Silicon Labs推出業(yè)界最低抖動的時鐘系列產(chǎn)品

- 高性能模擬與混合信號IC領(lǐng)導(dǎo)廠商Silicon Labs今日宣布針對高速網(wǎng)絡(luò)、通信和數(shù)據(jù)中心等當今互聯(lián)網(wǎng)基礎(chǔ)設(shè)施的根基,推出業(yè)界最高頻率靈活性和領(lǐng)先抖動性能的時鐘解決方案。Silicon Labs的新一代Si534x“片上時鐘樹“系列產(chǎn)品包括高性能時鐘發(fā)生器和高集成度Multi-PLL抖動衰減器。這些單芯片、超低抖動時鐘芯片整合了時鐘合成與抖動衰減功能,設(shè)計旨在減少光傳輸網(wǎng)絡(luò)、無線基礎(chǔ)設(shè)施、寬帶接入/匯聚、電信級以太網(wǎng)、測試和測量以及企業(yè)和數(shù)據(jù)中心設(shè)備(包括邊緣路由器、交換機、

- 關(guān)鍵字: Silicon Labs Si534x Multi-PLL

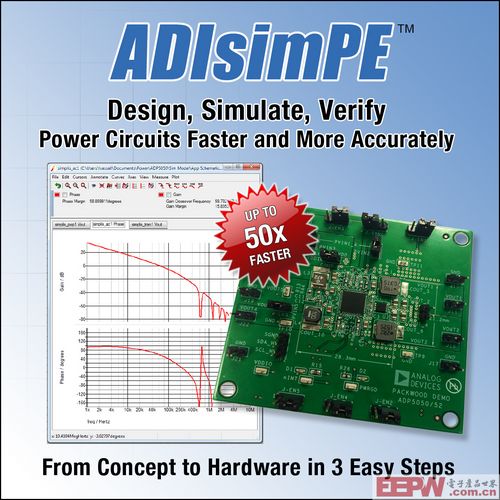

ADIsimPE確立電路速度、精度和虛擬原型開發(fā)標準

- Analog Devices, Inc.(ADI),全球領(lǐng)先的高性能信號處理解決方案提供商,最近推出了ADIsimPE?(個人版)仿真器,此款仿真器適合線性和混合信號應(yīng)用,能夠進行虛擬原型開發(fā),以滿足資源有限且要求產(chǎn)品快速上市的客戶的需求。ADIsimPE由SIMetrix/SIMPLIS?仿真器供電,它使用SIMetrix SPICE仿真線性電路,如精密基準電壓源、運算放大器和線性調(diào)節(jié)器以及SIMPLIS(分段線性系統(tǒng)仿真),從而高速分析PLL之類的非線性電路并且能夠切換電源

- 關(guān)鍵字: Analog Devices ADIsimPower PLL

德州儀器推出14GHz 分數(shù)N分頻鎖相環(huán)

- 日前,德州儀器 (TI) 宣布推出支持高級頻率調(diào)制功能的業(yè)界最高性能 14GHz 分數(shù) N分頻PLLatinum? 鎖相環(huán) (PLL)。該 LMX2492 提供業(yè)界最佳噪聲性能,比性能最接近的同類競爭器件低 6dB,可提升射頻 (RF) 靈敏度以及雷達覆蓋范圍及精確度。此外,該器件還支持 200MHz 的相位頻率檢測器、5V 充電泵電源以及 500 MHz 至 14GHz 的寬泛工作頻率。LMX2492 提供工業(yè)及汽車級(1 級)版本,適用于軍事與汽車雷達、微波回程、通信以及測量測試應(yīng)用。 LMX2

- 關(guān)鍵字: TI PLL LMX2492

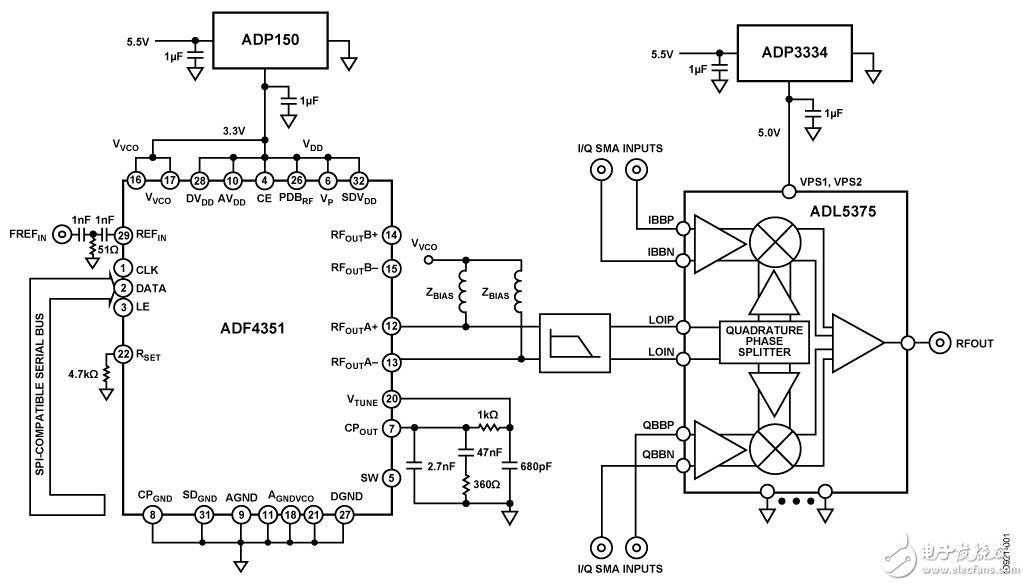

ADI發(fā)布三款全新的鎖相環(huán)(PLL)器件

- Analog Devices, Inc. (NASDAQ:ADI)近日發(fā)布三款全新的鎖相環(huán)(PLL)器件ADF5355/ADF4355-2/ADF4155,其中一款具有業(yè)界最寬的頻率覆蓋范圍和最低的壓控振蕩器(VCO)相位噪聲,且在單個器件中實現(xiàn)這些性能。ADF5355 PLL具有同類最寬的55 MHz至14 GHz頻譜范圍;而ADF4355-2 PLL的頻譜范圍為55 MHz至4.4 GHz。這些器件可供需要單片高性能寬帶頻率合成器的RF和微波通信系統(tǒng)設(shè)計人員使用。這兩款PLL均集成超低相位噪聲VC

- 關(guān)鍵字: ADI PLL ADF5355

IC時鐘分配系統(tǒng)中的PLL

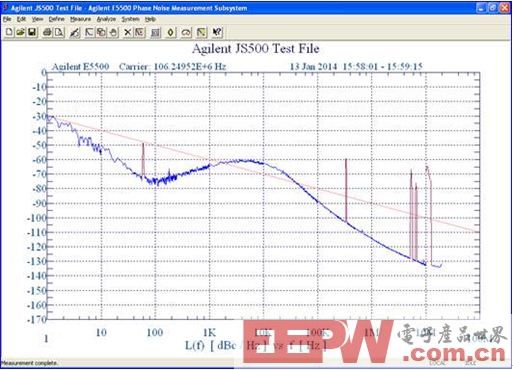

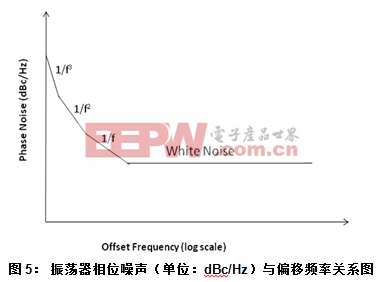

- 相位噪聲源: 振蕩器的單邊帶相位噪聲主要特性通常如圖5所示,該相位噪聲(單位:dBc/Hz)在對數(shù)尺度上被繪制成偏移頻率f0的函數(shù)。 實際曲線近似由一系列區(qū)間構(gòu)成,每一區(qū)間的斜率為1/fx,其中X=0表示白相位噪聲區(qū)間,即此時曲線斜率為0dB/decade。當X=1時,相位噪聲區(qū)間則稱為閃爍相位噪聲,其斜率為-20dB/decade。依此類推,其它區(qū)間則對應(yīng)更大的X值。X值越大的區(qū)間與載波頻率越接近。 圖6所示為PLL時鐘發(fā)生器中相位噪聲的曲線圖。需要注意的是,本圖與前述圖5中所示的

- 關(guān)鍵字: IC時鐘 PLL 噪聲 振蕩器 相位抖動

IC時鐘分配系統(tǒng)中的鎖相環(huán)

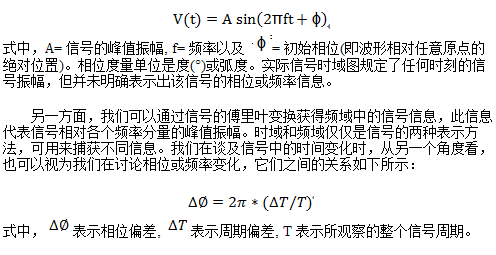

- 我們在本系列文章的前一部分[鏈接]已經(jīng)討論了鎖相環(huán)(PLL)的應(yīng)用以及在時鐘分配系統(tǒng)中,PLL相對于傳統(tǒng)振蕩器的優(yōu)勢。接下來我們將會闡述基于PLL的時鐘分配系統(tǒng)的重要參數(shù),這些參數(shù)都是設(shè)計時必須考慮的。例如,在實踐過程中,時鐘的準確時序?qū)λ蟹峙湎到y(tǒng)而言都非常重要。如果時鐘位置偏差范圍大,則可能會導(dǎo)致系統(tǒng)發(fā)生故障。時域中的這些偏差被稱為“抖動”。此外,抖動又分多個類別,譬如周期性抖動、周期間抖動、RMS抖動、長期抖動以及相位抖動。在本章節(jié),我們將重點闡述“相位抖動&

- 關(guān)鍵字: IC時鐘 PLL 噪聲 振蕩器 相位抖動

采用高性能時序幫助電路板設(shè)計人員工作

- 大部分電路板設(shè)計人員知道時鐘組件選擇并不簡單。好在設(shè)計并提供時序組件的大公司認識到客戶面臨的這一問題,提供工具支持設(shè)計人員迅速完成時鐘樹,并不要求設(shè)計人員是模擬設(shè)計PhD。讓我們看一下目前選擇并設(shè)計時鐘組件所需要處理的某些問題,討論完成每一項工作需要哪些幫助。在電路板設(shè)計流程中,時鐘提供服務(wù)功能以滿足體系結(jié)構(gòu)構(gòu)建模塊的要求。在選擇這些體系結(jié)構(gòu)組件之前,還無法確定所有的時鐘規(guī)范。注意,某些復(fù)雜的通信系統(tǒng)的確解決了體系結(jié)構(gòu)的一些時序功能問題,例如,網(wǎng)絡(luò)同步等。選擇了體系結(jié)構(gòu)單元后,電路板設(shè)計人員應(yīng)注意電源

- 關(guān)鍵字: 電路板 LED IDT PLL

STM32再學(xué)習(xí)——時鐘初始化

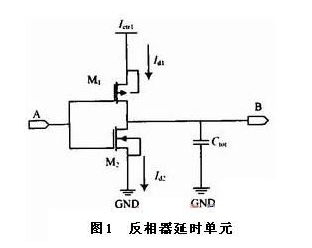

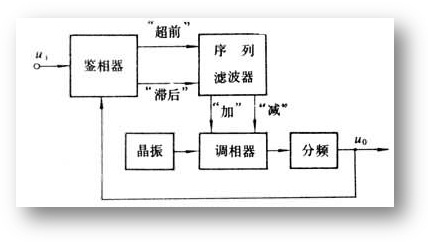

- STM32F系列微處理器,或者說是Cortex-M3內(nèi)核的MCU內(nèi),都集成了一個叫PLL的東西。PLL就是鎖相回路或鎖相環(huán)(Phase Locked Loop),用來統(tǒng)一整合時脈訊號,使內(nèi)存能正確的存取資料。PLL用于振蕩器中的反饋技術(shù),將外部的輸入信號與內(nèi)部的振蕩信號同步,鎖相環(huán)路的基本方框圖如下圖所示。一句話,PLL用來控制STM32F的時鐘頻率的。總而言之,STM32F系列MCU使用了這個東西,而我們在MCU上電之后,也就要對其正確的初始化,這樣,我們才能得到我們需要的時鐘配置。

- 關(guān)鍵字: 微處理器 STM32F PLL MCU 時鐘

pll介紹

魔方之PLL

PLL,(Permutation of Last Layer),魔方速度還原法CFOP的最后一步,是將最后一層的方塊移動到正確位置的一步。共有21個公式。(還有其他版本)

---------------------------------------------------------------------------------------------

PLL( [ 查看詳細 ]

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司