EEPW首頁(yè) >>

主題列表 >>

esl gaming

esl gaming 文章 最新資訊

面向FPGA的ESL工具

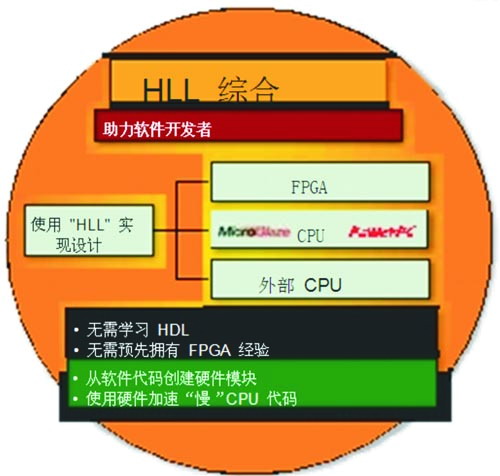

- 邏輯設(shè)計(jì)領(lǐng)域正發(fā)生著根本變化,新一代設(shè)計(jì)工具能夠幫助軟件開(kāi)發(fā)者將其算法表達(dá)直接轉(zhuǎn)換成硬件,而無(wú)需學(xué)習(xí)傳統(tǒng)的硬件設(shè)計(jì)技術(shù)。這些工具及相關(guān)設(shè)計(jì)方法學(xué)一起被歸類為電子系統(tǒng)級(jí) (ESL) 設(shè)計(jì),廣義上指從比目前主流的寄存器傳輸級(jí) (RTL) 更高的抽象級(jí)別上開(kāi)始的系統(tǒng)設(shè)計(jì)與驗(yàn)證方法學(xué)。與硬件語(yǔ)言如 Verilog 和 VHDL比起來(lái),ESL 設(shè)計(jì)語(yǔ)言在語(yǔ)法和語(yǔ)義上與流行的 ANSI C 比較接近。 ESL 與 FPGA 的關(guān)系 ESL 工具已經(jīng)存在了一段時(shí)間,而許多人覺(jué)得這些工具主要專注于 ASI

- 關(guān)鍵字: FPGA ESL

Synplicity加入Xilinx ESL的設(shè)計(jì)生態(tài)系統(tǒng)

- Synplicity® 公司日前宣布憑借其 Synplify® DSP 軟件加入了 Xilinx® ESL 計(jì)劃。Xilinx ESL 設(shè)計(jì)生態(tài)系統(tǒng)新增了 Synplify DSP 軟件,充分反映了 Xilinx 作為全球可編程解決方案領(lǐng)先供應(yīng)商在推進(jìn)技術(shù)創(chuàng)新與解決方案發(fā)展方面所作的努力,旨在不斷改進(jìn)高級(jí)電子系統(tǒng)級(jí) (ESL) 設(shè)計(jì)技術(shù)。Gary Smith EDA 的市場(chǎng)研究員 Gary Smith 認(rèn)為,ESL 設(shè)計(jì)是 EDA 市場(chǎng)中發(fā)展最快的領(lǐng)域之一,預(yù)計(jì)今后五年的復(fù)合年

- 關(guān)鍵字: 消費(fèi)電子 Synplicity Xilinx ESL DSP 消費(fèi)電子

面向FPGA的ESL工具

- 邏輯設(shè)計(jì)領(lǐng)域正在發(fā)生根本變化。新一代設(shè)計(jì)工具幫助軟件開(kāi)發(fā)者將其算法表達(dá)直接轉(zhuǎn)換成硬件,而無(wú)需學(xué)習(xí)傳統(tǒng)的硬件設(shè)計(jì)技術(shù)。 這些工具及相關(guān)設(shè)計(jì)方法學(xué)一起被歸類為電子系統(tǒng)級(jí) (ESL) 設(shè)計(jì),廣泛地指從比目前主流的寄存器傳輸級(jí) (RTL) 更高的抽象級(jí)別上開(kāi)始的系統(tǒng)設(shè)計(jì)與驗(yàn)證方法學(xué)。與硬件語(yǔ)言如 Verilog 和 VHDL比起來(lái),ESL 設(shè)計(jì)語(yǔ)言在語(yǔ)法和語(yǔ)義上與流行的 ANSI C 比較接近。 ESL 與 FPGA 有何關(guān)系? ESL 工具已經(jīng)存在了一段時(shí)間,而許多人覺(jué)得這些工具主要專注于 ASIC 設(shè)計(jì)

- 關(guān)鍵字: ESL FPGA 單片機(jī) 嵌入式系統(tǒng)

面向FPGA的ESL工具

- 邏輯設(shè)計(jì)領(lǐng)域正發(fā)生著根本變化,新一代設(shè)計(jì)工具能夠幫助軟件開(kāi)發(fā)者將其算法表達(dá)直接轉(zhuǎn)換成硬件,而無(wú)需學(xué)習(xí)傳統(tǒng)的硬件設(shè)計(jì)技術(shù)。這些工具及相關(guān)設(shè)計(jì)方法學(xué)一起被歸類為電子系統(tǒng)級(jí) (ESL) 設(shè)計(jì),廣義上指從比目前主流的寄存器傳輸級(jí) (RTL) 更高的抽象級(jí)別上開(kāi)始的系統(tǒng)設(shè)計(jì)與驗(yàn)證方法學(xué)。與硬件語(yǔ)言如 Verilog 和 VHDL比起來(lái),ESL 設(shè)計(jì)語(yǔ)言在語(yǔ)法和語(yǔ)義上與流行的 ANSI C 比較接近。 ESL 與 FPGA 的關(guān)系ESL 工具已經(jīng)存在了一段時(shí)間,而許多人覺(jué)得這些工具主要專注于 ASIC 設(shè)計(jì)流程。然

- 關(guān)鍵字: ESL FPGA 單片機(jī) 嵌入式系統(tǒng)

FPGA協(xié)同處理的優(yōu)勢(shì)

- 摘要: 本文介紹的ESL技術(shù)為傳統(tǒng)的DSP系統(tǒng)設(shè)計(jì)人員提供了有效的FPGA的設(shè)計(jì)實(shí)現(xiàn)方法。關(guān)鍵詞: DSP;FPGA;ESL 傳統(tǒng)的、基于通用DSP處理器并運(yùn)行由C語(yǔ)言開(kāi)發(fā)的算法的高性能DSP平臺(tái),正在朝著使用FPGA預(yù)處理器和/或協(xié)處理器的方向發(fā)展。這一最新發(fā)展能夠?yàn)楫a(chǎn)品提供巨大的性能、功耗和成本優(yōu)勢(shì)。盡管優(yōu)勢(shì)如此明顯,但習(xí)慣于使用基于處理器的系統(tǒng)進(jìn)行設(shè)計(jì)的團(tuán)隊(duì),仍會(huì)避免使用FPGA,因?yàn)樗麄內(nèi)狈Ρ匾挠布寄埽瑏?lái)將FPGA用作協(xié)處理器(圖1)。不熟悉像VHDL和Verilog這樣

- 關(guān)鍵字: 0611_A DSP ESL FPGA 單片機(jī) 嵌入式系統(tǒng) 雜志_技術(shù)長(zhǎng)廊

esl gaming介紹

您好,目前還沒(méi)有人創(chuàng)建詞條esl gaming!

歡迎您創(chuàng)建該詞條,闡述對(duì)esl gaming的理解,并與今后在此搜索esl gaming的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對(duì)esl gaming的理解,并與今后在此搜索esl gaming的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢有限公司