- 隨著筆記本電腦、手機、PDA 等移動設備的普及,對應各種電池電源使用的集成電路的開發越來越活躍,高性能、低成本、超小型封裝產品正在加速形成商品化。LDO(低壓差)型線性穩壓器由于具有結構簡單、成本低廉、低噪聲、

- 關鍵字:

設計 穩壓器 線性 CMOS 超低

- 焊接絕緣柵(或雙柵)場效應管以及CMOS集成塊時,因其輸入阻抗很高、極間電容小,少量的靜電荷即會感應靜電高壓,導致器件擊穿損壞。筆者通過長期實踐摸索出下述焊接方法,取得令人滿意的效果。1.焊絕緣柵場效應管。

- 關鍵字:

CMOS 焊 場效應管 集成電路

- CCD(Charge Coupled Device)圖像傳感器(以下簡稱CCD)和CMOS圖像傳感器(CMOS Image Sensor以下簡稱CIS)的主要區別是由感光單元及讀出電路結構不同而導致制造工藝的不同。CCD感光單元實現光電轉換后,以電荷的方

- 關鍵字:

傳感器 對比 圖像 CCD CMOS 監控

- CCD(ChargeCoupledDevice)圖像傳感器(以下簡稱CCD)和CMOS圖像傳感器(CMOSImageSensor以下簡稱CIS)的主要...

- 關鍵字:

CMOS 圖像傳感器 CCD 圖像傳感器 CIS

- 威盛電子在1月4日推出VIA VL810 SuperSpeed集群控制器,這是USB3.0技術時代業內首款支持更高傳輸速度的整合單芯片解決方案。

USB3.0(即超速USB)的最大數據傳輸速度可達5Gbps,是現有USB2.0設備傳輸速度的10倍;此外,該技術還能提高外部設備與主機控制器之間的互動功能,包括能耗管理上的重要改進。

VIA VL810由威盛集團全資子公司VIA Labs研發,它實現在一個USB接口上連接多個設備從而擴展了計算機的USB性能。一個輸出接口及四個輸入接口不僅支持高

- 關鍵字:

威盛 USB3.0 CMOS

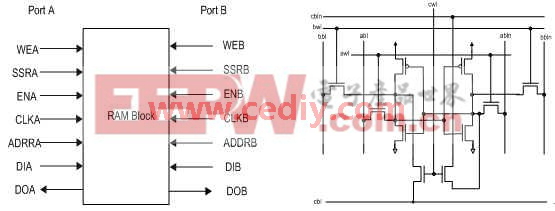

- 基于0.13微米CMOS工藝下平臺式FPGA中可重構RAM模塊的一種設計方法,1. 引言

對于需要大的片上存儲器的各種不同的應用,FPGA 需要提供可重構且可串聯的存儲器陣列。通過不同的配置選擇,嵌入式存儲器陣列可以被合并從而達到位寬或字深的擴展并且可以作為單端口,雙端口

- 關鍵字:

RAM 重構 模塊 設計 方法 FPGA 平臺 0.13 微米 CMOS 工藝

- 0 引 言

隨著集成電路技術的廣泛應用及集成度的不斷增加,超大規模集成電路(VLSI)的功耗、芯片內部的溫度不斷提高,溫度保護電路已經成為了眾多芯片設計中必不可少的一部分。本文在CSMC 0.5/μm CMOS工藝下,

- 關鍵字:

電路 保護 溫度 CMOS 功能

- IBM研究人員開發出了基于極薄SOI(ETSOI)的全耗盡CMOS技術,面向22nm及以下節點。

在IEDM會議上,IBM Albany研發中心的Kangguo Cheng稱該FD-ETSOI工藝已獲得了25nm柵長,非常適合于低功耗應用。除了場效應管,IBM的工程師還在極薄SOI襯底上制成了電感、電容等用于制造SOC的器件。

該ETSOI技術包含了幾項工藝創新,包括源漏摻雜外延淀積(無需離子注入),以及提高的源漏架構。

該技術部分依賴于近期SOI晶圓供應商推出了硅膜厚度為6nm的S

- 關鍵字:

IBM CMOS 22nm SOC

- 鎖相環在通訊技術中具有重要的地位,在調制、解調、時鐘恢復、頻率合成中都扮演著不可替代的角色。可控振蕩器是鎖相環的核心部分。最近,鑒于對集成電路低功耗和高集成度的追求,越來越多的研究人員投人到基于CMOS工

- 關鍵字:

CMOS 高頻 壓控振蕩器

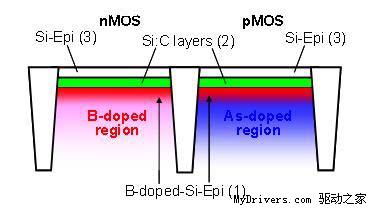

- 東芝公司今天在美國馬里蘭州巴爾的摩市舉行的IEDM半導體技術會議上宣布,其20nm級CMOS工藝技術獲得了重大突破,開啟了使用體硅CMOS工藝制造下一代超大規模集成電路設備的大門,成為業界首個能夠投入實際生產的20nm級CMOS工藝。東芝表示,他們通過對晶體管溝道的摻雜材料進行改善,實現了這次突破。

在傳統工藝中,由于電子活動性降低,通常認為體硅(Bulk)CMOS在20nm級制程下已經很難實現。但東芝在溝道構造中使用了三層材料,解決了這一問題,成功實現了20nm級的體硅CMOS。這三層材料

- 關鍵字:

東芝 CMOS 20nm

- 0 引言

電源管理技術近幾年已大量應用于便攜式和手提電源中。電源管理系統包括線性穩壓器、開關穩壓器和控制邏輯等子系統。本文主要針對低壓差線性穩壓器進行研究。低壓差線性穩壓器是電源管理系統中的一個基

- 關鍵字:

穩壓器 設計 線性 CMOS 集成 高性能

cmos+dps介紹

您好,目前還沒有人創建詞條cmos+dps!

歡迎您創建該詞條,闡述對cmos+dps的理解,并與今后在此搜索cmos+dps的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473