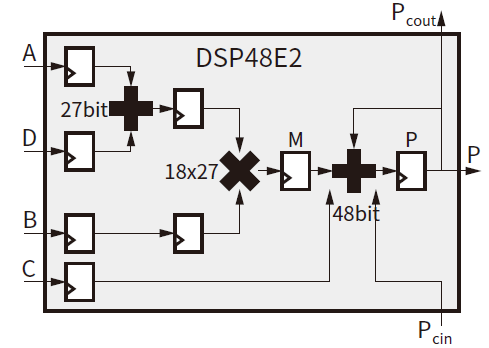

- 接上期http://www.104case.com/article/202009/418351.htm賽靈思 DSP 片上的 INT4 優化使用 DSP 硬件資源可實現乘法和累加 (MAC) 占用硬件資源較少。經優化后,DSP 能夠在 16nm 或 28nm 器件上處理盡可能多的 MAC 運算。以 16nm 為例,賽靈思可編程器件中 UltraScale? 架構的 DSP48E2 片就屬于專用片[參考資料 11]。DSP48E2 片由一個 27x18 二進制補碼乘法器和一個 48 位累加器構成。如圖 3

- 關鍵字:

賽靈思 INT4 卷積神經網絡

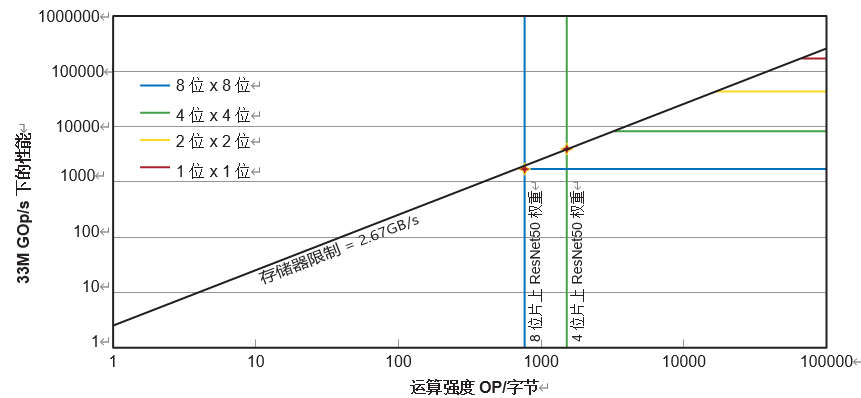

- ?對于 AI 推斷,在提供與浮點相媲美的精度的同時,INT8 的性能優于浮點。然而在資源有限的前提下,INT8 卻不能滿足性能要求,INT4 優化則是解決之道。通過 INT4 優化,與現有的 INT8 解決方案相比,賽靈思在實際硬件上可實現高達 77% 的性能提升。概要賽靈思在其硬件平臺上提供 INT8 AI 推斷加速器 — 深度學習處理器單元 (XDPU)。然而,在某些資源受限,要求高性能、低時延的場景(例如對資源、功耗敏感的邊緣側場景和低時延 ADAS 場景)中,為了實現比 INT8 更低的

- 關鍵字:

賽靈思 INT4 卷積神經網絡

int4介紹

您好,目前還沒有人創建詞條int4!

歡迎您創建該詞條,闡述對int4的理解,并與今后在此搜索int4的朋友們分享。

創建詞條

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473