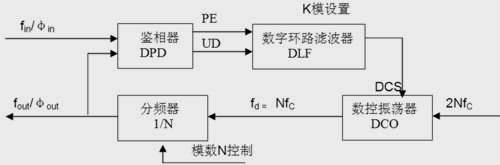

- 本文簡要介紹了在FPGA中實現全數字鎖相環(DPLL)的原理與方法,以解決在同步串行數據通信時的同步時鐘不穩定時的快速恢復問題; 并重點介紹了采用可控模數分頻器實現的數字鎖相環中寬頻帶捕獲的方法與實現過程。

- 關鍵字:

DPLL FPGA 數字環路濾波器 時鐘恢復 寬頻帶

數字環路濾波器介紹

環路濾波器的性能優劣會直接影響到跟蹤環路的性能。而采用數字化的環路濾波器便于調試參數和提高系統可靠性。環路濾波器的輸出要直接控制頻率合成器產生相應頻率,使本地偽碼能夠準確跟蹤發端信息。

基本原理:

數字環中使用的數字環路濾波器與模擬環中使用的環路濾波器作用一樣,都對噪聲及高頻分量起抑制作用,并且控制著環路相位校正的速度與精度。適當選擇濾波器的參數,可以改善環路的性能。數字環路濾波器的設計原 [

查看詳細 ]

關于我們 -

廣告服務 -

企業會員服務 -

網站地圖 -

聯系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產品世界》雜志社 版權所有 北京東曉國際技術信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網安備11010802012473