前道工序 文章 最新資訊

引入空氣間隙以減少前道工序中的寄生電容

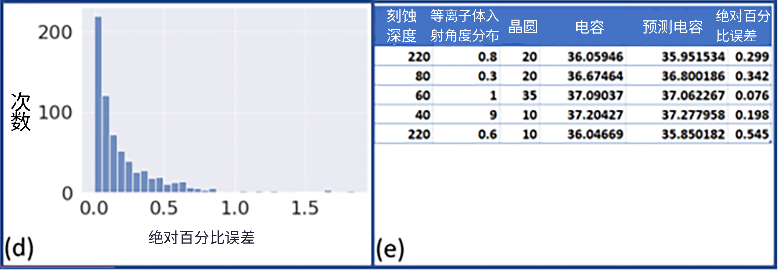

- 減少柵極金屬和晶體管的源極/漏極接觸之間的寄生電容可以減少器件的開關(guān)延遲。減少寄生電容的方法之一是設(shè)法降低柵極和源極/漏極之間材料層的有效介電常數(shù),這可以通過在該位置的介電材料中引入空氣間隙來實現(xiàn)。這種類型的方式過去已經(jīng)用于后道工序 (BEOL) 中,以減少金屬互連之間的電容[1-4]。本文中,我們將專注于前道工序 (FEOL),并演示在柵極和源極/漏極之間引入空氣間隙的SEMulator3D?模型[5]。SEMulator3D?是一個虛擬的制造軟件平臺,可以在設(shè)定的半導(dǎo)體工藝流程內(nèi)模擬工藝變量。利用SE

- 關(guān)鍵字: 空氣間隙 前道工序 寄生電容

| 共1條 1/1 1 |

前道工序介紹

您好,目前還沒有人創(chuàng)建詞條前道工序!

歡迎您創(chuàng)建該詞條,闡述對前道工序的理解,并與今后在此搜索前道工序的朋友們分享。 創(chuàng)建詞條

歡迎您創(chuàng)建該詞條,闡述對前道工序的理解,并與今后在此搜索前道工序的朋友們分享。 創(chuàng)建詞條

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國際技術(shù)信息咨詢有限公司