EEPW首頁(yè) >>

主題列表 >>

信號(hào)完整性

信號(hào)完整性 文章 最新資訊

信號(hào)完整性----最優(yōu)化導(dǎo)通孔高速串聯(lián)應(yīng)用

- 在低頻率的時(shí)候,導(dǎo)通孔的影響不大。但在高速系列連接中,導(dǎo)通孔會(huì)毀了整個(gè)系統(tǒng)。這篇專(zhuān)欄將描繪一個(gè)簡(jiǎn)單的導(dǎo)通孔建模與仿真過(guò)程,從中你認(rèn)識(shí)可以得到優(yōu)化設(shè)計(jì)一些關(guān)鍵點(diǎn)。

- 關(guān)鍵字: 信號(hào)完整性 導(dǎo)通孔 高速串聯(lián) 差分過(guò)孔

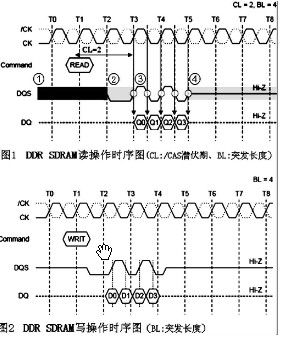

汽車(chē)音響導(dǎo)航系統(tǒng)高速DDR200 PCB的信號(hào)完整性設(shè)計(jì)

- 本文主要介紹在汽車(chē)音響導(dǎo)航系統(tǒng)中使用的高速DDR200,在兼顧高速電路的基本理論和專(zhuān)業(yè)化設(shè)計(jì)經(jīng)驗(yàn)的指導(dǎo)下, 保證信號(hào)完整性的PCB設(shè)計(jì)方法。

- 關(guān)鍵字: 高速信號(hào) GHz數(shù)量級(jí) 信號(hào)完整性

基于HyperLynx的數(shù)字電路設(shè)計(jì)綜合仿真方法

- 針對(duì)數(shù)字電路系統(tǒng)設(shè)計(jì)中存在的信號(hào)完整性、散熱、電磁兼容性(EMC)等問(wèn)題,結(jié)合HyperLynx仿真軟件提出了一種綜合仿真方法。通過(guò)雷達(dá)信號(hào)處理機(jī)的設(shè)計(jì)實(shí)例,詳細(xì)描述了HyperLynx各仿真模塊的功能和特點(diǎn),為數(shù)字電路系統(tǒng)設(shè)計(jì)與仿真提供了重要參考。

- 關(guān)鍵字: 綜合仿真 HyperLynx 信號(hào)完整性

基于高速嵌入式系統(tǒng)的信號(hào)完整性分析

- 提高信號(hào)完整性、減小串?dāng)_和反射是高速電路系統(tǒng)設(shè)計(jì)能否成功的關(guān)鍵。本文基于以ARM1176JZF-S S3C6410為核處理器的嵌入式開(kāi)發(fā)系統(tǒng),對(duì)高速電路進(jìn)行了研究。通過(guò)信號(hào)完整性仿真分析,解決了DDR SDRAM差分時(shí)鐘信號(hào)的反射問(wèn)題和視頻輸出信號(hào)的串?dāng)_問(wèn)題。

- 關(guān)鍵字: 信號(hào)完整性 串?dāng)_ 反射

高速PCB過(guò)孔的研究

- 在數(shù)字通信系統(tǒng)中,隨著PCB布線密 度,布線層數(shù)和傳輸信號(hào)速率的不斷增加,信號(hào)完整性的問(wèn)題變得越來(lái)越突出,已經(jīng)成為高速PCB設(shè)計(jì)者巨大的挑戰(zhàn)。而在高速PCB設(shè)計(jì)中,過(guò)孔已經(jīng)越來(lái)越普 遍使用,其本身的寄生參數(shù)極易造成信號(hào)完整性問(wèn)題,如何減少過(guò)孔本身所產(chǎn)生的信號(hào)完整性問(wèn)題,已經(jīng)成為高速PCB設(shè)計(jì)者研究的重點(diǎn)和難點(diǎn)。

- 關(guān)鍵字: 高速PCB 過(guò)孔 寄生電容 反焊盤(pán) 信號(hào)完整性

高速設(shè)計(jì)中的信號(hào)完整性和電源完整性分析

- 引言:信號(hào)完整性和電源完整性是兩種不同但領(lǐng)域相關(guān)的分析,涉及數(shù)字電路正確操作。在信號(hào)完整性中,重點(diǎn)是確保傳輸?shù)?在接收器中看起來(lái)就像 1(對(duì)0同樣如此)。在電源完整性中,重點(diǎn)是確保為驅(qū)動(dòng)器和接收器提供足夠

- 關(guān)鍵字: 信號(hào)完整性 電源完整性

信號(hào)完整性――最優(yōu)化導(dǎo)通孔高速串聯(lián)應(yīng)用

- 在低頻率的時(shí)候,導(dǎo)通孔的影響不大。但在高速系列連接中,導(dǎo)通孔會(huì)毀了整個(gè)系統(tǒng)。在某些情況下,在3.125Gbps的時(shí)候,他們可以采用一個(gè)樣子不錯(cuò)的,寬的孔眼。在5 Gbps的時(shí)候?qū)⑺兂梢粋€(gè)支柱。了解引起導(dǎo)通孔限制的根

- 關(guān)鍵字: 信號(hào)完整性 導(dǎo)通孔 高速串聯(lián) 差分過(guò)孔

解決信號(hào)完整性問(wèn)題的100條通用設(shè)計(jì)原則(干貨)

- 具有40年研究經(jīng)驗(yàn)的國(guó)際大師Eric Bogatin給出的:100條使信號(hào)完整性問(wèn)題最小化的通用設(shè)計(jì)原則 No.1 網(wǎng)絡(luò)信號(hào)質(zhì)量問(wèn)題最小化 策略---保持信號(hào)在整個(gè)路徑中感受到的瞬態(tài)阻抗不變。 設(shè)計(jì)原則: 1. 使用可控之阻抗布線。 2. 理想情況下,所有的信號(hào)應(yīng)使用低電平平面作為參考平面。 3. 若使用不同的電壓平面作為信號(hào)的參考平面,則這些平面之間必須是緊耦合。為此,用最薄的介質(zhì)材料將不同的電壓平面隔開(kāi),幷使用多個(gè)傳感量小的去耦合電容。 4. 使用2D場(chǎng)求

- 關(guān)鍵字: 信號(hào)完整性

Teledyne LeCroy信號(hào)完整性學(xué)術(shù)專(zhuān)家Eric Bogatin榮獲DesignCon2016工程師年度獎(jiǎng)

- Teledyne?LeCroy今天宣布Teledyne?LeCroy信號(hào)完整性學(xué)術(shù)專(zhuān)家,Eric?Bogatin博士,被DesignCon?2016授予年度工程師獎(jiǎng)。該獎(jiǎng)項(xiàng)是對(duì)行業(yè)專(zhuān)家針對(duì)芯片設(shè)計(jì)/測(cè)試,單板或系統(tǒng)設(shè)計(jì)的領(lǐng)導(dǎo)力,創(chuàng)造力,以及杰出的打破常規(guī)能力的認(rèn)可。該獎(jiǎng)項(xiàng)由NI發(fā)起,在DesignCon?2016上提出,并在1月19日-21日?qǐng)?zhí)行。 “我非常激動(dòng)和榮幸被選為年度工程師。從提名到最終結(jié)果,都是一件興奮的事。我感到很榮幸身處于擁有如此多專(zhuān)

- 關(guān)鍵字: Teledyne 信號(hào)完整性

PCB布線6大原則

- 1 電源、地線的處理 既使在整個(gè)PCB板中的布線完成得都很好,但由于電源、 地線的考慮不周到而引起的干擾,會(huì)使 ...

- 關(guān)鍵字: 地線 PCB 信號(hào)完整性

信號(hào)完整性大師Eric博士宣布25年來(lái)最后一次系列課程

- 2013.7.8 - Bogatin Enterprises, Teledyne LeCroy的一個(gè)機(jī)構(gòu),作為業(yè)內(nèi)最知名的培訓(xùn)和出版物企業(yè),致力于幫助工程師將復(fù)雜的信號(hào)完整性問(wèn)題轉(zhuǎn)化為實(shí)際的設(shè)計(jì)解決方案,日前發(fā)布了它25年來(lái)的最后一期課程。該信號(hào)完整性課程已經(jīng)在世界范圍內(nèi)教授了二十余年,參與課程的工程師超過(guò)10,000名。

- 關(guān)鍵字: Bogatin 力科 信號(hào)完整性

Bogatin發(fā)布最后一期信號(hào)完整性課程

- Bogatin Enterprises,作為業(yè)內(nèi)最知名的培訓(xùn)和出版物企業(yè),幫助工程師將復(fù)雜的信號(hào)完整性問(wèn)題轉(zhuǎn)化為實(shí)際的設(shè)計(jì)解決方案,日前發(fā)布了它的最后一期課程。信號(hào)完整性課程已經(jīng)在世界范圍內(nèi)教授了二十余年,參與課程的工程師超過(guò)10,000名。

- 關(guān)鍵字: Bogatin 力科 信號(hào)完整性

高速電路之信號(hào)回流路徑分析

- 摘要:在高速數(shù)字系統(tǒng)電路設(shè)計(jì)中,電磁兼容性、信號(hào)完整性和電源完整性等問(wèn)題緊密的交織在一起,成為高速電路設(shè)計(jì)的挑戰(zhàn)。信號(hào)線與信號(hào)回流路徑之間的位置與電磁兼容性、信號(hào)完整性問(wèn)題有著直接的關(guān)系,處理好信號(hào)線

- 關(guān)鍵字: 高速電路 信號(hào)回流路徑 電磁兼容 信號(hào)完整性

利用IBIS模型研究信號(hào)完整性問(wèn)題

- 本文是關(guān)于在印刷電路板 (PCB) 開(kāi)發(fā)階段使用數(shù)字輸入/輸出緩沖信息規(guī)范 (IBIS) 模擬模型的文章。本文將介紹 ...

- 關(guān)鍵字: IBIS 模型研究 信號(hào)完整性

基于IBIS建模仿真分析的信號(hào)完整性問(wèn)題探討

- 高速數(shù)字設(shè)計(jì)人員面臨的一個(gè)挑戰(zhàn)就是處理其電路板上的過(guò)沖、下沖、錯(cuò)配阻抗振鈴、抖動(dòng)分布和串?dāng)_問(wèn)題。這些問(wèn)題都可歸入信號(hào)完整性范疇。許多高速設(shè)計(jì)人員都使用輸入/輸出緩沖信息規(guī)范 (IBIS) 建模語(yǔ)言來(lái)預(yù)見(jiàn)并解決信

- 關(guān)鍵字: IBIS 建模 仿真分析 信號(hào)完整性

信號(hào)完整性介紹

信號(hào)完整性

信號(hào)完整性是指信號(hào)在傳輸路徑上的質(zhì)量,傳輸路徑可以是普通的金屬線,可以是光學(xué)器件,也可以是其他媒質(zhì)。信號(hào)具有良好的信號(hào)完整性是指當(dāng)在需要的時(shí)候,具有所必需達(dá)到的電壓電平數(shù)值。差的信號(hào)完整性不是由某一單一因素導(dǎo)致的,而是板級(jí)設(shè)計(jì)中多種因素共同引起的。

中文名信號(hào)完整性

實(shí) 質(zhì)指信號(hào)在傳輸路徑上的質(zhì)量

多種因素差的信號(hào)完整性

包 括數(shù)字示波器、 [ 查看詳細(xì) ]

熱門(mén)主題

關(guān)于我們 -

廣告服務(wù) -

企業(yè)會(huì)員服務(wù) -

網(wǎng)站地圖 -

聯(lián)系我們 -

征稿 -

友情鏈接 -

手機(jī)EEPW

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

京ICP備12027778號(hào)-2 北京市公安局備案:1101082052 京公網(wǎng)安備11010802012473

Copyright ?2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《電子產(chǎn)品世界》雜志社 版權(quán)所有 北京東曉國(guó)際技術(shù)信息咨詢(xún)有限公司