基于Xtensa的ASIP開(kāi)發(fā)流程研究

前言

本文引用地址:http://www.104case.com/article/95269.htm隨著半導(dǎo)體工藝技術(shù)向著納米尺度的發(fā)展,微電子技術(shù)進(jìn)入SoC(系統(tǒng)芯片)時(shí)代,且沿著可靠性強(qiáng)、體積小、功耗低等方向繼續(xù)發(fā)展。在下一代SoC設(shè)計(jì)流程中,系統(tǒng)級(jí)EDA工具的地位變得比以往更加重要,ESL(Electronic System Level)設(shè)計(jì)方法學(xué)將是設(shè)計(jì)下一代SoC的關(guān)鍵,因?yàn)橹饾u縮短的上市時(shí)間需要硬件-軟件并行設(shè)計(jì)。

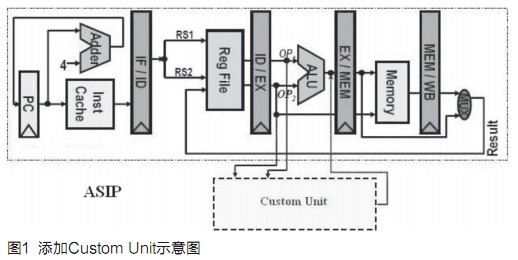

本文以Tensilica Xtensa可配置、可擴(kuò)展處理器為開(kāi)發(fā)平臺(tái),探索了高性能低功耗ASIP(Application Specific Instruction-set Processor專(zhuān)用指令處理器)開(kāi)發(fā)流程。

ASIP設(shè)計(jì)理論

面向特定應(yīng)用的ASIP處理器,既有ASIC執(zhí)行特定應(yīng)用的高效性,又有GPP處理器可編程的靈活性,能夠簡(jiǎn)化設(shè)計(jì)復(fù)雜度、縮短設(shè)計(jì)周期、加快上市步伐,在SoC設(shè)計(jì)中得到了廣泛的應(yīng)用。如何快速高效地定制ASIP,使其滿足運(yùn)算性能、芯片面積、上市時(shí)間和功耗等要求,是一個(gè)極具挑戰(zhàn)性的問(wèn)題。設(shè)計(jì)者需要在ASIP指令集設(shè)計(jì)過(guò)程中在廣泛的設(shè)計(jì)空間進(jìn)行指令集探索,尋找滿足設(shè)計(jì)約束的處理器體系結(jié)構(gòu)[1-8]。因此迫切需要可以支持快速ASIP設(shè)計(jì)的行為級(jí)設(shè)計(jì)方法和合適的EDA工具。

評(píng)論