從PCIe探索彈性緩沖器真義

下面以兩個耳熟能詳的接口為例,來說明彈性緩沖器一般位于控制器中的確切位置。

本文引用地址:http://www.104case.com/article/9144.htm彈性緩沖器在不同接口中的位置

首先以USB2.0 Hub為例。眾所周知,Hub裝置的職責就是承上啟下,單進多出,以擴展連接設備的數量。USB接口最多可連接127個設備。而USB2.0的Hub又有別于上一代USB1.1規格,它將收進來的封包去頭去尾,只讀取數據本身,然后以局部新的干凈時鐘信號將它輸出。因此,480Mbps可連續接5階Hub裝置依然保持480Mbps數據傳送暢通。

所以,USB2.0 Hub內部的重發器(Repeater)區塊通常內含彈性緩沖器,可用來補償Rcv_Clk及Xmt_Clk兩個時鐘信號差。

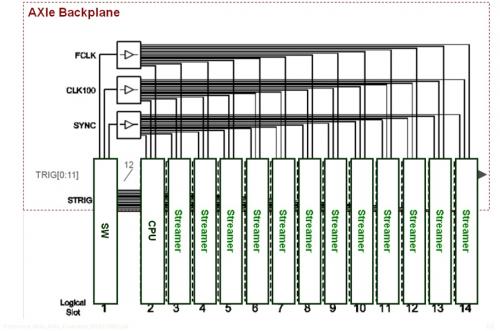

再以PCI Express為例。PCI Express采用內置時鐘的8b/10b編碼方式,因此在接收端勢必要構建一個時鐘數據回復CDR(Clock Data Recovery)回路,其中的彈性緩沖器也用來補償傳送時鐘f1與接收端時鐘f2的差異。

邏輯上,因為FIFO兩端的時鐘存在差異,最后很有可能發生溢位(Overflow)或下溢(Underflow)現象。為了避免這種情況,EB彈性緩沖器通常會在特定的時間插入或移除特殊的符號(Symbol)。如此一來,用來補償兩端時鐘的差異就不用考慮額外的問題了。這也是EB彈性緩沖器名稱的由來。

彈性緩沖器的出現甚至可以回溯到60年代。1963年,Maurice Karnaugh獲得這個技術的專利,只不過當時的應用是在PCM電話網絡上。當高速傳輸轉向串行方式時,EB彈性緩沖器的價值再度顯現。

PCIe中的時鐘差

PCI Express采用的8b/10b編碼,輸出端與接收端時序的同步關系可看成是一種“源同步”,也是一種“時鐘傳遞”的數據傳輸協議方法。這與過去的PCI或PCI-X采用的共通時鐘方式是截然不同的。

為了方便記憶起見,最為簡單的方法就是將“源同步”看成時鐘與數據的合成,都來自于輸出端的驅動器就可以了。

PCI Express的傳輸速率是 2.5Gbps(波特率),容許的誤差范圍是

評論