SSI接口技術及其在音頻處理中的應用

隨著嵌入式系統的廣泛應用,系統內串口通信的需求越來越高,串行數據傳輸的協議也多樣化,常用的有SSI、SPI、I2C、UART等。其中,SSI是一種帶有幀同步信號的串行數據協議。微處理器MCF5329中的SSI接口除了能用作一般的串行數據傳輸外,由于它帶有的幀同步信號可用作左右聲道數據的同步,支持兩種音頻總線接口(I2S和AC97接口),所以它還能用作音頻數據的傳輸。

TLV320DAC23是TI公司推出的高性能立體聲高端編解碼芯片,支持多種采樣率和多種音頻格式,并具有功耗低、封裝小的特點,廣泛應用于便攜式數字音頻處理系統中。

1 同步串行接口SSI的工作原理

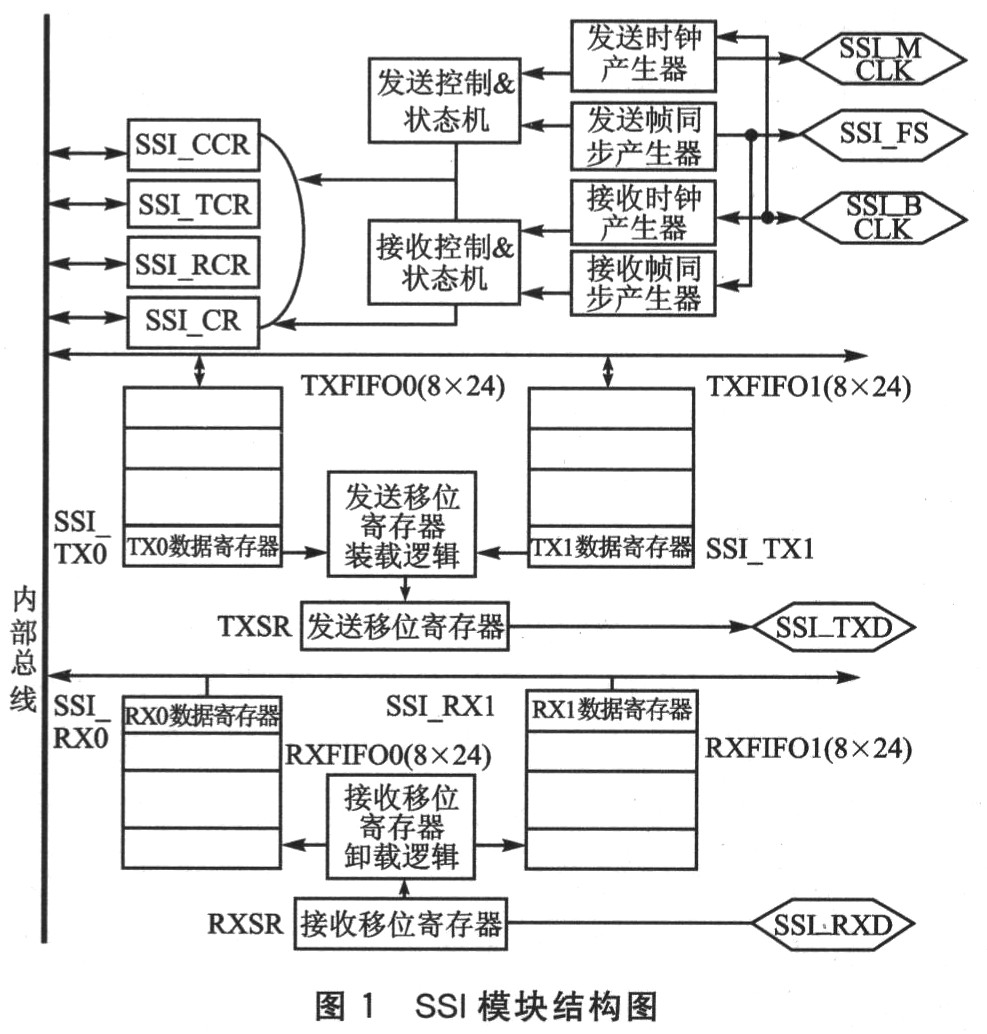

Synchronous SerialInterface(SSI)是一個全雙工的串行接口,允許芯片與多種串行設備通信。它是高精度絕對值角度編碼器中一種較常用的接口方式,它采用主機主動式讀出方式,即在主控者發出的時鐘脈沖的控制下,從最高有效位(MSB)開始同步傳輸數據。SSI模塊結構如圖1所示。

從圖中可看出,SSI模塊由發送電路、接收電路、串行時鐘和幀同步時鐘產生電路組成。發送電路和接收電路相互獨立,但是共用串行時鐘和幀同步時鐘。

1.1 SSI模塊引腳信號描述

SSLCLKIN:SSI時鐘輸入信號。

SSLBCLK:SSI串行比特時鐘。

SSLMCLK:SSI串行主時鐘信號,在SSI主模式下,

該信號也作為過采樣時鐘信號。

SSI_FS:SSI串行幀同步信號。

SSLRXD:SSI串行接收數據信號。

SSI_TXD:SSI串行發送數據信號。

1.2 SSI的操作模式

SSI有3種基本同步操作模式:普通模式、網絡模式和門時鐘模式。

普通模式是最簡單的模式,一幀內只能傳輸一個字,而且每一幀都需要幀同步信號來控制同步;網絡模式主要用于多時隙的情況下,一幀內可以傳輸2個字到32個字不等;門時鐘SSI_BCLK模式下,串行比特時鐘SSI_BCLK指示了發送引腳或接收引腳上的有效數據,所以不需要幀同步信號。

除了上述3種基本模式外,針對音頻上的應用,SSI還支持兩種衍生模式——I2S模式和AC97模式,分別用于傳輸I2S和AC97音頻格式數據。

1.3 SSI的初始化

初始化SSI模塊的正確順序:

①上電或重啟SSI(SSI_CR[SSI_EN]=0),即關閉SSI模塊功能。

②配置SSI模塊。涉及的寄存器包括控制寄存器SSI_CR、中斷允許寄存器SSI_IER、發送配置寄存器SSI_TCR、接收配置寄存器SSI_RCR和時鐘控制寄存器SSI_CCR。

③通過SSI_IER寄存器設置必要的中斷或DMA。

④設置SSI_CR[SSI_EN]=1允許SSI模塊功能。

⑤設置SSI_CR[TE/RE],開始發送/接收數據。

1.4 SSI的工作過程

(1)發送數據

單通道時,數據從串行發送數據寄存器SSI_TX0中傳到發送移位寄存器TXSR中,再通過串行發送引腳SSI_TXD發送出去,然后根據用戶設置情況決定是否產生發送中斷。如果發送緩沖區TXFIFOO被允許,則SSI_TX0繼續從TXFIFOO中取數據,直到TXFIFOO中的數據全部被發送,再通過用戶設置情況決定是否產生發送中斷。雙通道時,發送移位寄存器TXSR交替從SSI_TX0

和SSI_TXl中取出數據。

(2)接收數據

單通道時,數據從串行接收引腳SSI_RXD進來,由接收移位寄存器RXSR傳輸給接收數據寄存器SSI_RX0,再根據用戶設置情況決定是否產生接收中斷。如果接收緩沖區RXFIFOO被允許,則SSI_RX0將數據寫入RXFIFOO,并繼續從接收移位寄存器中獲取數據。雙通道時,接收移位寄存器RXSR交替將數據傳輸給SSI_RX0和SSI_RXl。

2 音頻編解碼芯片簡介

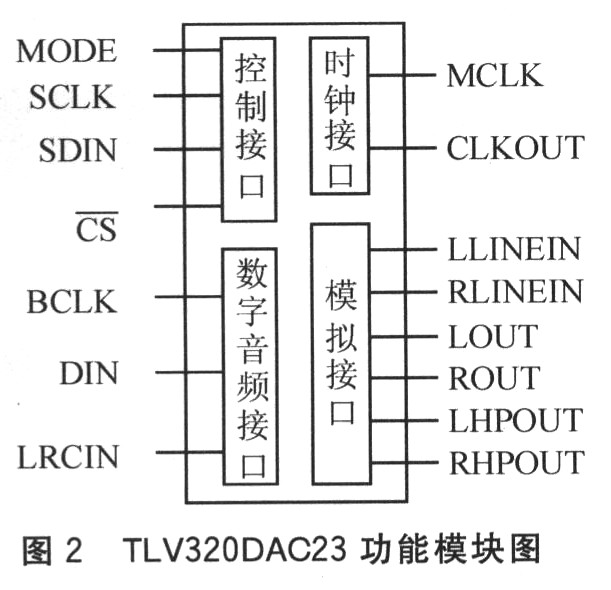

TLV320DAC23是TI公司推出的一顆高性能立體聲音頻處理芯片(CODEC芯片),采用了多比特sigma-delta過采樣技術,采樣率可以從8 kHz到96 kHz,傳輸字長可選擇為16位、20位、24位或32位;最大輸出信噪比可達到100 dB;控制端口可兼容SPI、2-wire等協議;回放模式下功率為18 mw,省電模式下小于15μW;適用于便攜式的數字音頻處理。其功能模塊框圖如圖2所示。

2.1 控制接口

控制接口用于對器件TLV320DAC23的寄存器編程,設置音頻芯片的工作參數。它兼容兩種模式:SPI三線模式和2一wire模式。

MODE:模式選擇引腳。為0時,采用2一wire模式;為1時,采用SPI模式。

SCLK:控制端口串行數據時鐘。

SDI:控制端口串行數據輸入。

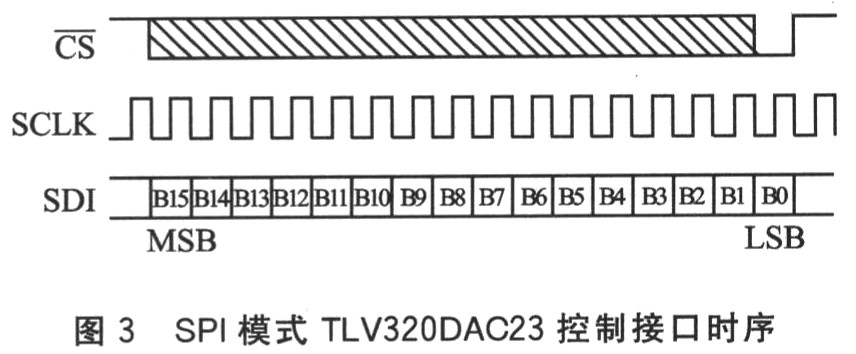

CS:控制端口輸入鎖存/地址選擇。在SPI模式下,CS用于數據鎖存控制;在2一wire模式下,CS定義了器件地址域的第7位。SPI模式下,一個控制字為16位,分為兩部分:高7位為控制地址,低9位為控制字。16位的控制字由MSB位開始傳輸,每個比特在SCLK的上升沿被鎖存,整個16位的控制字在最低位被CS鎖存進TLV320DAC23。操作時序如圖3所示。其中,B[15:9]為控制地址,B[8:O]為控制字。

2.2 模擬接口

模擬接口包括線輸入、線輸出和耳機輸出。耳機輸出可以驅動16Ω或32 Ω的耳機,音量增益為6 dB到一73 dB。

LLINEIN、RLINEIN:左、右聲道輸入。

LOUT、ROUT:左、右聲道輸出。

LHPOUT、RHPOUT:左、右聲道耳機輸出

2.3 數字音頻接口

數字音頻接口用于輸入TLV320DAC23的D/A數據。

BCLK:I2S串行比特時鐘。主模式時BCLK為輸出,從模式時BCLK為輸入。

DIN:I2S串行數據輸入。

LRCIN:字時鐘信號(幀信號),用于控制左、右聲道的數據。在主模式中,由TLV320DAC23產生該信號,在從模式中,由主設備(如DSP或MCU)產生該信號。

TLV320DAC23支持4種音頻接口模式:右對齊模式、左對齊模式、I2S模式和DSP模式。這4種模式都是最高有效位MSB在前,16到32位不同的字長(右對齊除外,它不支持32位)。圖4是I2S模式下的數字音頻接口時序,數據的MSB在LRCIN下降沿后的第2個BCLK上升沿開始傳輸。

2.4 時鐘接口

MCLK:芯片主時鐘信號。當TLV320DAC23作為主設備時,該信號由芯片自身產生;當TLV320DAC23作為從設備時,該信號由外部產生。

CLKOUT:時鐘輸出信號。可以為MCLK或MCLK/2。

3 基于MCF5329的音頻驅動設計

3.1 硬件電路

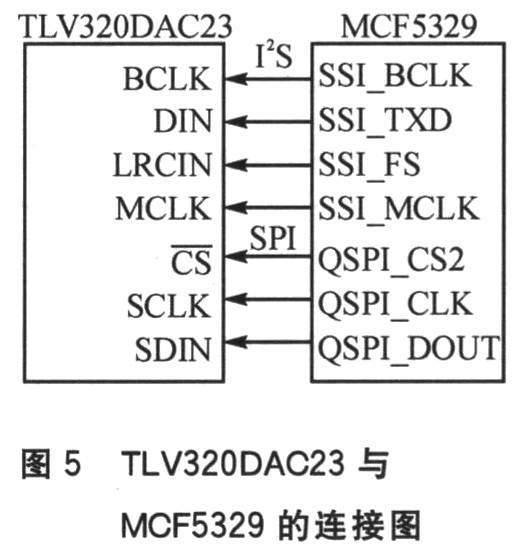

TLV320DAC23與MCF5329的接口有兩個:一個是控制接口,用于設置TLV320DAC23的寄存器,從而設置它的工作參數。由于MCF5329具有QSPI模塊,它兼容SPI接口格式,所以TLV320DAC23的控制接口采用SPI模式。另一個是數字音頻接口,用于傳輸TLV320DAC23的音頻數據并控制數據的時序。由于MCF5329的SSI模塊支持I2S音頻格式,所以TLV320DAC23的數字音頻接口采用I2S模式。

在本設計中,由微控制器MCF5329提供時鐘信號,所以將MCF5329設為主設備,TLV320DAC23作為從設備。具體連接如圖5所示。

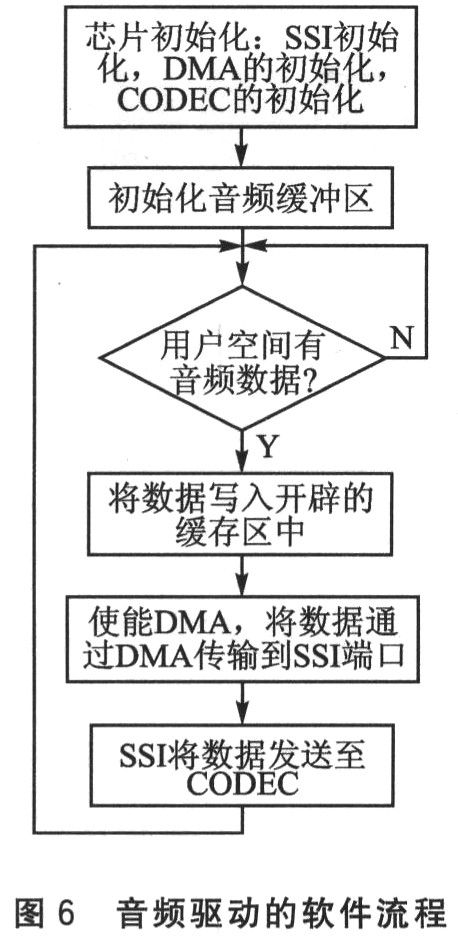

3.2 軟件設計

音頻播放的過程如下:程序檢測到用戶空間有需要播放的音頻數據,便將音頻數據拷貝到所建立的緩沖區中;然后通過DMA將緩沖區的音頻數據傳輸到SSI模塊的發送引腳SSI_TXD,發送引腳將數據發送至TLV320DAC23中,通過耳機播放出來。

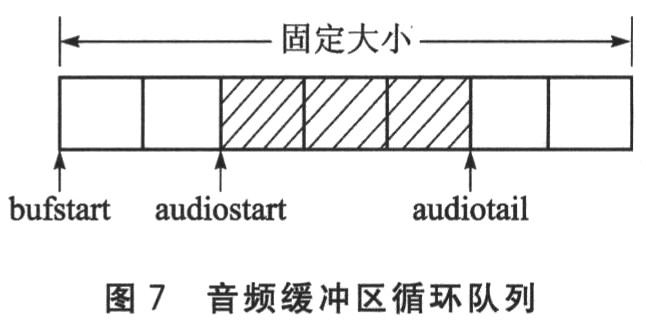

軟件設計的流程如圖6所示。其中,音頻緩沖區被設置為一個固定大小的循環隊列,其設置如圖7所示。初始時,bufstart、audiostart、audiotail都指向緩沖區頭。當用戶空間有數據時,將數據拷貝到緩沖區并用audiotail指示數據尾部,數據的頭部通過DMA引擎連接到SSI_TXD引腳,隨著數據被SSI_TXD發送至TLV320DAC23,audiostart跟蹤數據的頭部。

結 語

本文分析了同步串行接口SSI的工作原理及過程,并通過與編解碼芯片TLV320DAC23的通信詳細介紹了SSI在音頻處理中的應用。實踐表明,SSI接口簡單,使用靈活可靠。

評論