基于AX88796B的網絡接口模塊的設計與實現

引言

本文引用地址:http://www.104case.com/article/86294.htm網絡技術應用日益普及的今天,工業現場的儀器儀表、數據采集和控制設備也日趨網絡化,工業自動化和網絡的結合越來越密切。而將以太網和嵌入式系統相結合應用于工業控制中已成為趨勢。

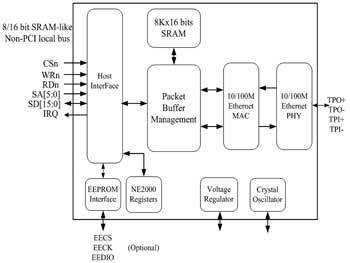

AX88796B是Asix公司推出的一款為嵌入式和工業以太網應用而設計的低引腳數以太網控制芯片。其內部集成10/100Mb/s自適應的介質訪問層MAC和物理層收發器PHY以及8K×16位的SRAM。AX88796B可應用于商業級0~70C和工業級-40C~85C的溫度范圍。AX88796B支持MCS-51系列、80186系列、ISA總線和SRAM-like接口類型。執行基于IEEE802.3/IEEE802.3u局域網標準的10Mb/s和100Mb/s以太網控制功能,并且提供發送隊列功能來增強標準NE2000的發送性能。

AT91R40008微控制器是基于ARM7TDMI核的32位RISC結構的嵌入式微控制器,非常適于工業實時控制應用。AX88796B引腳的LQFP封裝減少了PCB空間并且和NE2000兼容,編程簡單,其驅動可以容易快速的移植到許多嵌入式系統中。因此,綜合上述兩種芯片的優點,我們選擇AX88796B和AT91R40008作為工業實時控制中嵌入式網絡應用的解決方案,具有很好的工業應用價值和前景。

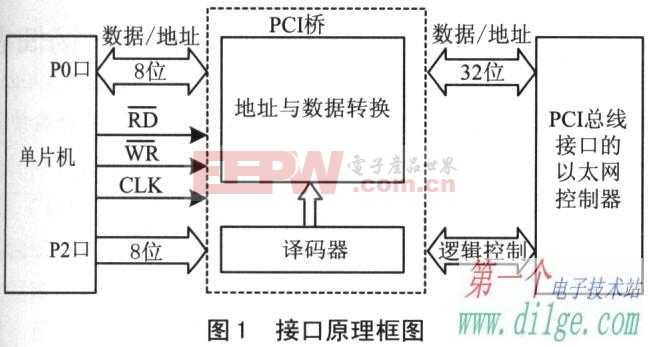

圖1 AX88796B內部結構圖

AX88796B內部結構及工作原理

1 AX88796B的內部結構

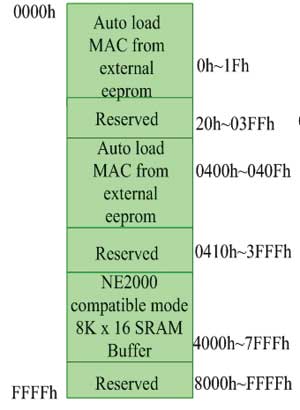

網卡上電復位時EEPROM接口能夠通過CSR中偏移為14H的SMI/EEPROM寄存器來存取數據,MAC地址由EEPROM中讀取,并被自動載入地址為0000h~001fh和0400h~040fh的內部存儲區中。如果沒有使用EEPROM,每次上電對網卡進行初始化時候就手動給它分配一個MAC地址。

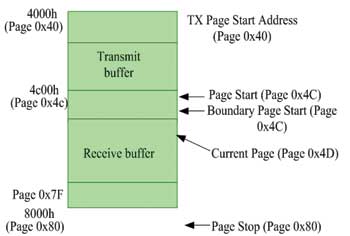

AX88796B內部有一個16KB(0x4000~0x7fff)大小的SRAM,該SRAM是雙端口SRAM,可以同時被網卡讀寫和用戶讀寫,這片地址空間的一部分被保留用來存放一個緩沖環結構,另一部分可以給用戶使用。在本設計中,16KB的SRAM全部被用來接收和發送數據包。本地DMA正是通過這個緩沖環結構來接收報文的。這個結構由一連串相鄰的固定長度為256B的緩沖區構成,每256字節稱為一頁,共有64頁。頁的地址就是地址的高8位,頁地址為0x00~0xff。其中0x40~0x4B為網卡的發送緩沖區,共12頁,剛好可以存儲2個最大的以太網包,所以我們把發送緩沖區分成兩部分進行輪流發送。使用0x4c~0x7f共52頁為網卡的接收緩沖區。AX88796B的SRAM空間結構和收發緩沖區結構如圖2、3所示。

圖2 SRAM空間結構

圖3 收發緩沖區

2 AX88796B的工作原理

由四個寄存器來控制接收緩沖區的操作。Page Start Address Register (PSTART)和Page Stop Address Register(PSTOP)定義了接收緩沖區的起始和終止頁號,形成一個接收緩沖環。當前頁地址寄存器(Current Page Register)指向第一個用于存儲數據包的緩沖區。邊界指針寄存器(Boundary Pointer Register)指向在緩沖環中第一個未被主機讀取的數據包。如果本地DMA地址與Boundary Pointer Register的值相等,則接收過程中止。邊界指針也被用來初始化遠端DMA來移動一個數據包,當數據包被移走后,邊界指針也向前增長。這樣,Current Page Register如同一個寫指針,Boundary Pointer如同一個讀指針。接收到一個數據包時,從PSR中指定的頁號開始存儲,如果一個256B的緩沖區不夠,DMA會執行一個前向連接來連接下一個緩沖區以存儲這個數據包的剩余部分。連接的時候緩沖區必須是連續的,一個數據包總是會被存儲在相鄰的緩沖區里。在連接下一個緩沖區前,緩沖管理邏輯會執行兩個比較,首先比較下一個緩沖區的DMA地址是否和page Stop Register相等,若相等,則DMA地址被恢復為page start address register中保存的地址。其次和boundary pointer register比較,如果相等,則接收報文過程終止。Boundary Pointer Register能夠防止緩沖區里的數據還沒有讀出就被重寫。

要發送和接收數據包就必須通過DMA讀寫AX88796B內部的SRAM。DMA分為遠程DMA(Remote DMA)和本地DMA(Local DMA)。CPU從網卡的SRAM讀寫數據稱為遠端DMA。AX88796B讀寫SRAM稱為本地DMA。數據包的接收過程:當數據包到達網卡的MAC層后,本地DMA先將到達MAC層的報文傳送到網卡的內存中,主機CPU再通過遠端DMA通道從網卡內存中讀取數據包。數據包的發送過程:主機CPU通過遠端DMA把要發送的數據包送到網卡的內存中,本地的DMA將該數據包傳送到MAC層,再經由內部的PHY層發送至網絡。

網絡接口硬件設計

1 AX88796B的引腳配置

AX88796B與CPU的連接方式有MCS51模式、ISA模式、186模式,此方案使用了ISA 8bit模式。片選引腳CSn,讀寫信號RDn、WRn、RSTn都是低電平有效,分別和AT91r40008相應引腳相連即可。AX88796B的數據線SD0~SD15和AT91r40008的DATA[0:15]相連,可通過軟件配置為16位或8位DMA數據傳輸方式。AX88796B的IRQ是可編程的,中斷請求信號可以通過配置BTCR或EEPROM來選擇其觸發方式和中斷I/O緩沖類型,AT91r40008中斷觸發方式應該和BTCR的配置相一致。其他重要引腳如IOIS16、PME、EECE、EECK在本設計中懸空處理。引腳配置應根據網卡芯片手冊說明和設計方案而定。

對AX88796B控制狀態寄存器(CSR)的操作,需要確定其基地址,基地址的選擇應根據AT91r40008的可編程外部總線EBI的地址和片選信號來確定。AT91r40008的EBI處理位于地址空間0x00400000~0xFFC00000的訪問操作,在訪問過程中,它將產生外部器件的控制訪問信號。當把網卡寄存器地址空間映射進EBI后,直接對EBI地址空間操作即可控制網卡的寄存器讀寫。對每個映射進EBI接口的外圍器件,可以編程等待周期數、數據浮空時間、數據總線寬度(8位或16位)等。

linux操作系統文章專題:linux操作系統詳解(linux不再難懂)

評論