采用SAR結構的8通道12位ADC設計單片機

引言

ADC是模擬系統與數字系統接口的關鍵部件,長期以來一直被廣泛應用于通信、軍事及消費電子等領域。隨著計算機和通信產業的迅猛發展,ADC在便攜式設備上的應用發展迅速,正逐步向高速、高精度和低功耗的方向發展。

ADC是采樣速率低于5MSPS的中高分辨率應用的常見結構,由于其實質上采用的是二進制搜索算法,內部電路可以運行在幾MHz,采樣速率主要由逐次逼近算法確定。

本文基于上華0.6mm BiCMOS工藝設計了一個8通道12位串行輸出ADC,轉換核心電路采用逐次逼近型結構,并在總結改進傳統結構的基礎上,采用了電壓定標和電荷定標的復合式DAC結構。這種“5+4+3”的分段式復合結構不但避免了大電容引入的匹配性問題,而且由于引入了電阻,減小了電路本身的線性誤差。比較器的實現采用多級級聯的放大器結構,降低了設計復雜度。最后基于CSMC 0.6mm BiCMOS工藝實現了整體版圖設計。

系統結構

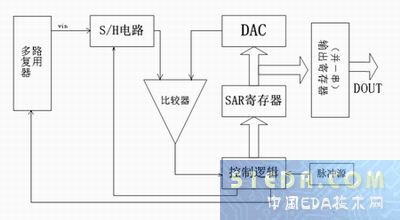

SAR ADC電路結構主要包含五個部分:采樣保持電路、比較器、DAC、逐次逼近寄存器和邏輯控制單元。轉換中的逐次逼近是按對分原理,由控制邏輯電路完成的。其工作過程如下:啟動后,控制邏輯電路首先把逐次逼近寄存器的最高位置1,其它位置0,將其存儲到逐次逼近寄存器,然后經數模轉換后得到一個電壓值(大小約為滿量程輸出的一半)。這個電壓值在比較器中與輸入信號進行比較,比較器的輸出反饋到DAC,并在下一次比較前對其進行修正。即輸入信號的抽樣值與DAC的初始輸出值相減,余差被比較器量化,量化值再來指導控制邏輯是增加還是減少DAC的輸出;然后,再次從輸入抽樣值中減去這個新的DAC輸出值。不斷重復這個過程,直至完成最后一位數字的實現。由此可見,這種數據的轉變始終處于邏輯控制電路的時鐘驅動之下,逐次逼近寄存器不斷進行比較和移位操作,直到完成最低有效位(LSB)的轉換。這時逐次逼近寄存器的各位值均已確定,轉換操作完成。

由于本設計針對的是串行多路通道轉換技術,所以本文在SAR ADC基本結構的基礎上,在模擬輸入前端加入多路復用模塊,并在輸出后端加入并/串轉換電路。

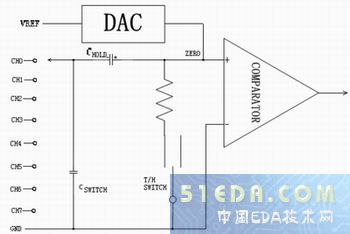

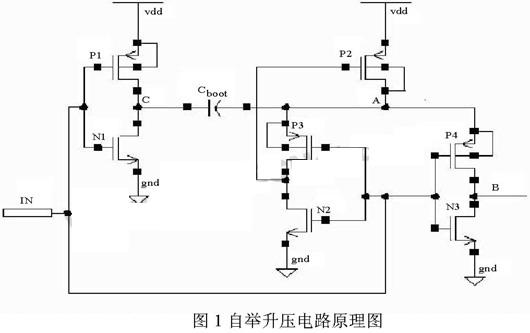

圖1 整體結構簡圖和輸入等效電路

為實現信號的快速精確轉換,SAR ADC中重要部件是采樣保持電路、比較器和DAC,等效輸入電路如圖1所示。在獲取數據期間,被選信道作為輸入給電容CHOLD充電,獲取時間結束后,T/H開關打開,電荷維持在CHOLD上作為信號樣本,與DAC中產生的模擬信號進行比較,將比較結果輸入并/串輸出寄存器,在三態總線控制下輸出數字位。

電路設計與實現

采樣/保持電路的性能高低限定了整個ADC的速度和精度,在設計中采用雙差分底板采樣技術,雙差分結構以獲得優良的AC性能,另外底板采樣技術的應用也極大地減小了電荷注入、時鐘饋通以及有限帶寬所造成的誤差,優化了整體性能。其中比較器的實現采用3個放大器級聯結構,這樣不僅極大提高了增益,而且減小了比較器的設計難度,提高了電路性能。下面重點講述DAC的設計與實現。

SAR ADC的速度和分辨率主要受反饋電路中DAC的速度、分辨率和線性的限制,精確設計DAC是本次設計的重點和關鍵。傳統的SAR ADC多采用簡單的電阻分壓式或電容電荷型結構來實現。電阻分壓式轉換器的優點是只需要用到一種電阻,容易保證制造精度,即使電阻出現較大的誤差,也不會出現非單調性。但n位二進制輸入的電阻分壓式數模轉換器需要2n個分壓電阻以及同樣數量的模擬開關,所以隨著位數的增加,其所需元器件的數量會呈幾何級數增加,這是它的缺點。單獨用這種結構來做一個DAC的情況比較少見,但是它卻在8位以下的SAR ADC中常用到。電容電荷型DAC的優點是精度較高,但缺點是面積大,對寄生電容敏感,而且還需要兩相時鐘,增加了設計制造的復雜度。

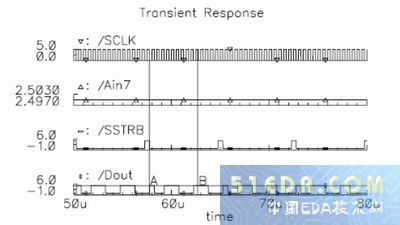

圖2 第8通道對2.5V電壓進行轉換的輸出波形

本文設計的DAC采用復合結構。由于本芯片是一個12位精度的ADC,要求DAC也要達到12位精度,而且對于位數較高的轉換器,從芯片面積和性能方面綜合考慮,組合結構較單一結構優勢顯著。因而本文采用5+3+4復合結構實現,即高5位MSB采用電容網絡實現,中間3位采用電阻網絡,而低4位LSB仍用電容網絡實現,這樣設計避免了不同結構實現上的不足,結合了各自的優點,較好的實現電路設計目標。此DAC的優點是具有一定的單調性,因為電阻串本質上是單調的,而且3個數字位只有一種阻值的電阻,不存在電阻失配問題。電阻串不需要預充電,轉換速度比電容陣列的轉換速度快,但芯片占用面積較大;電容網絡最多只需滿足5位數字位對應的電容精度要求便可實現12位轉換匹配。所以在分配每段位數時,本文在芯片面積和轉換速度之間進行了折中考慮。單獨對DAC進行仿真得到其建立時間僅為12ns。

設計仿真

根據電路功能及指標要求,在Cadence環境下用Hspice對電路進行仿真。通過控制邏輯精確控制,最后實現12位數字的轉換結果,圖2為選擇第8通道對2.5V電壓進行轉換的輸出波形,實現了模擬信號到數字信號的正確轉換。12位ADC的工作溫度范圍為-55℃~125℃,仿真條件為VDD=5.0V,VSS=0V,VREF=4.096V,VAGND=0V。最后基于CSMC 0.6mm BiCMOS工藝完成了版圖設計,面積為2.5×2.2mm2。

結語

本文基于CSMC 0.6mm BiCMOS工藝設計實現了一個12位串行輸出ADC,采用電壓定標和電荷定標組合式數模轉換器技術,比較器的實現采用多級級聯放大器形式,通過合理的時序控制,實現了較好的性能,轉換速率為7.5ms,正常工作電流2.8mA,增益誤差小于2LSB,線性誤差小于1個LSB,最后版圖面積為2.5×2.2mm2,此轉換器對于消費電子、汽車電子及便攜式產品等方面應用是具有較好性價比的選擇。

參考文獻:

1 Kh.handidi, Vincent S.Tso. An 8-b 1.3-MHz Successive-Approximation A/D Converter. IEEE J. Solid-State Circuits,1990,25(3)

2 T.P.Redfern et al.. A monolithic charge-balancing successive-approximation A/D technique. IEEE J. Solid-State Circuits,

1979, SC-14: 912-920

3 Richard K.Hester et al. Fully Differential ADC with Rail-to-Rail Common-Mode Range and Nonlinear Capacitor Compensation. IEEE J.

評論