TTL“或”擴展器和“與或非”門

——

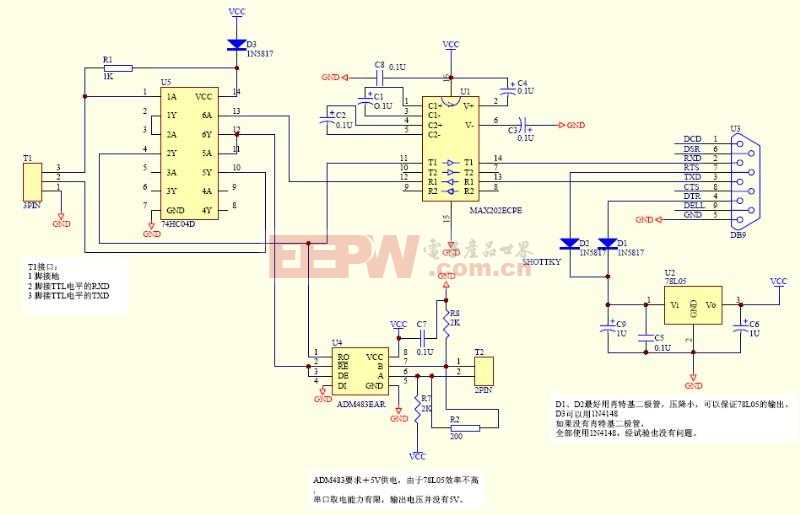

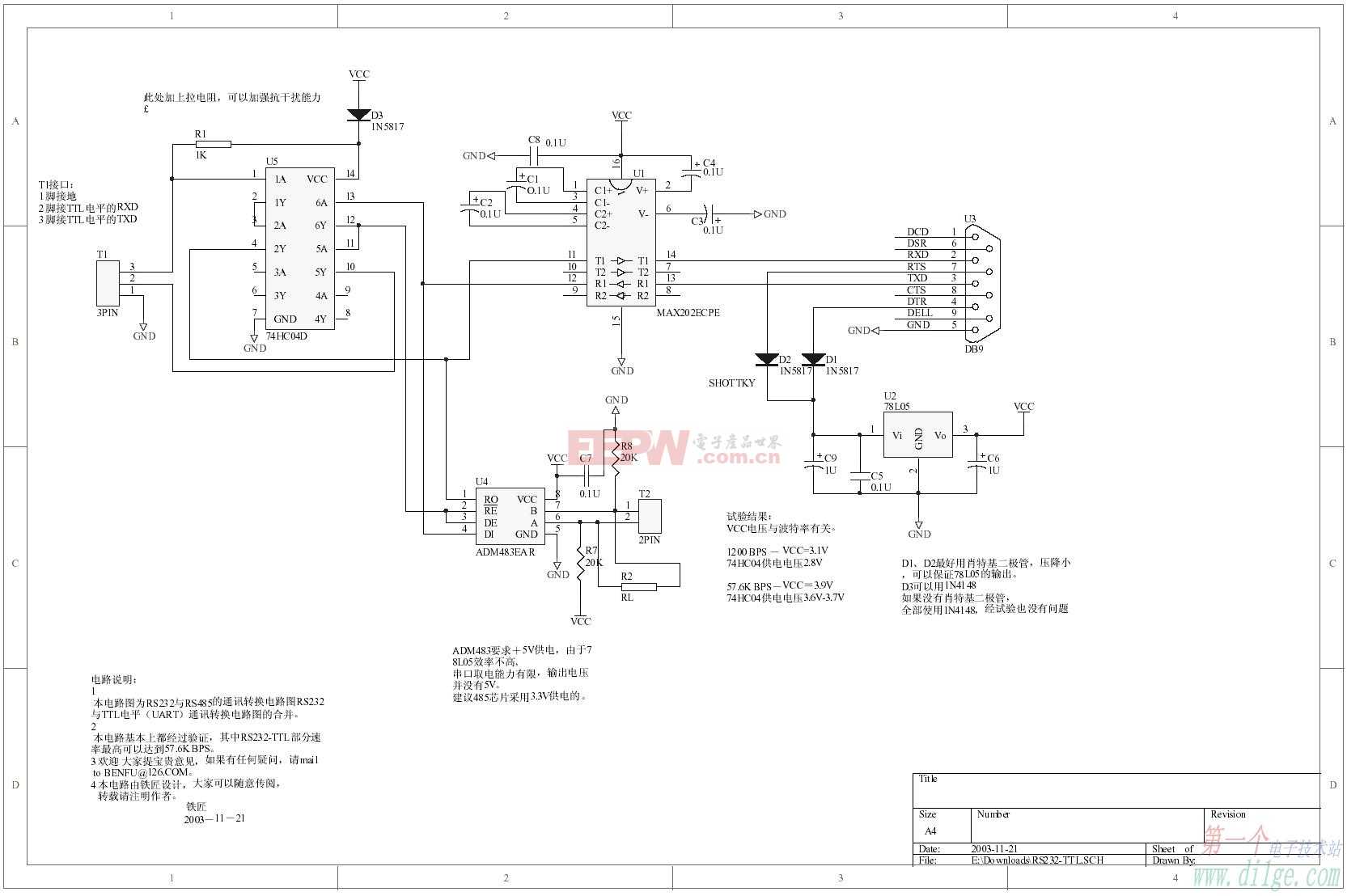

若只用“與非”門實現(xiàn)函數(shù)![]() ,則需要圖1(a)所示的邏輯圖。該方法所用門的個數(shù)較多,級數(shù)也多。故可用增加“或”擴展器的方法來實現(xiàn)。“或”擴展器的具體電路如圖1(b)所示。

,則需要圖1(a)所示的邏輯圖。該方法所用門的個數(shù)較多,級數(shù)也多。故可用增加“或”擴展器的方法來實現(xiàn)。“或”擴展器的具體電路如圖1(b)所示。

圖1 ![]() 邏輯圖及“或”擴展器電路 圖2 4,3,2,2“與或非”門邏輯符號

邏輯圖及“或”擴展器電路 圖2 4,3,2,2“與或非”門邏輯符號

使用時,將圖1(b)輸出端c、e分別和“與非”門VT2(如圖3所示)管的集電極和發(fā)射極相接,由此就可使原來的“與非”門變成了“與或非”門,“與或非”門的符號如圖1(c)中所示,其輸出F的邏輯表達式在該圖中也已輸出。

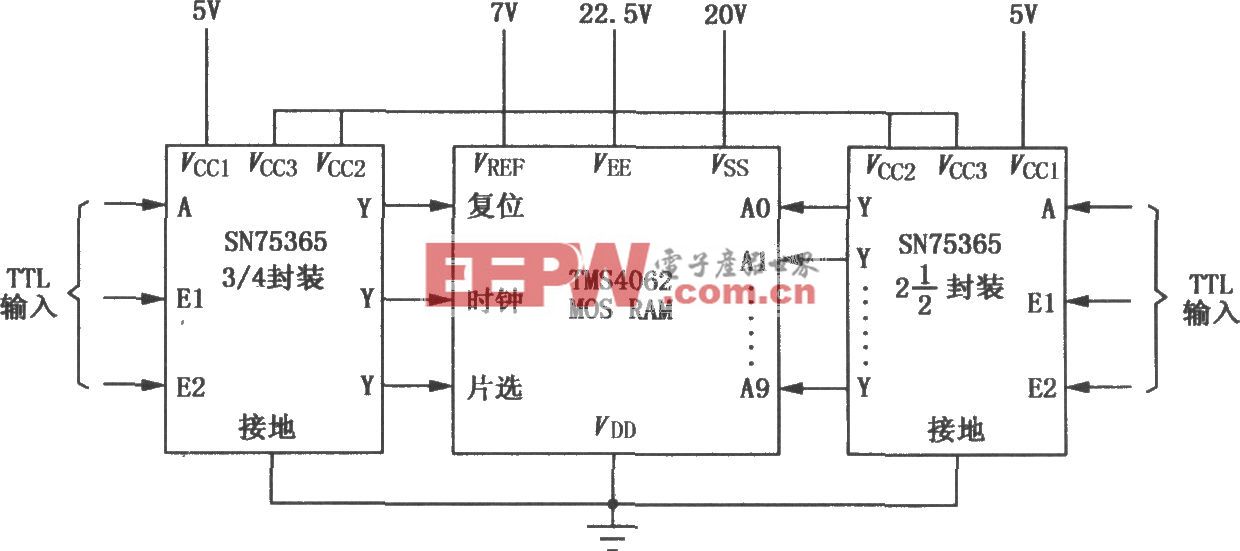

現(xiàn)在有各種型號的“與或非”門產(chǎn)品,圖2所示的一種被稱為4,3,2,2“與或非”門,其輸出邏輯表達式為:

![]()

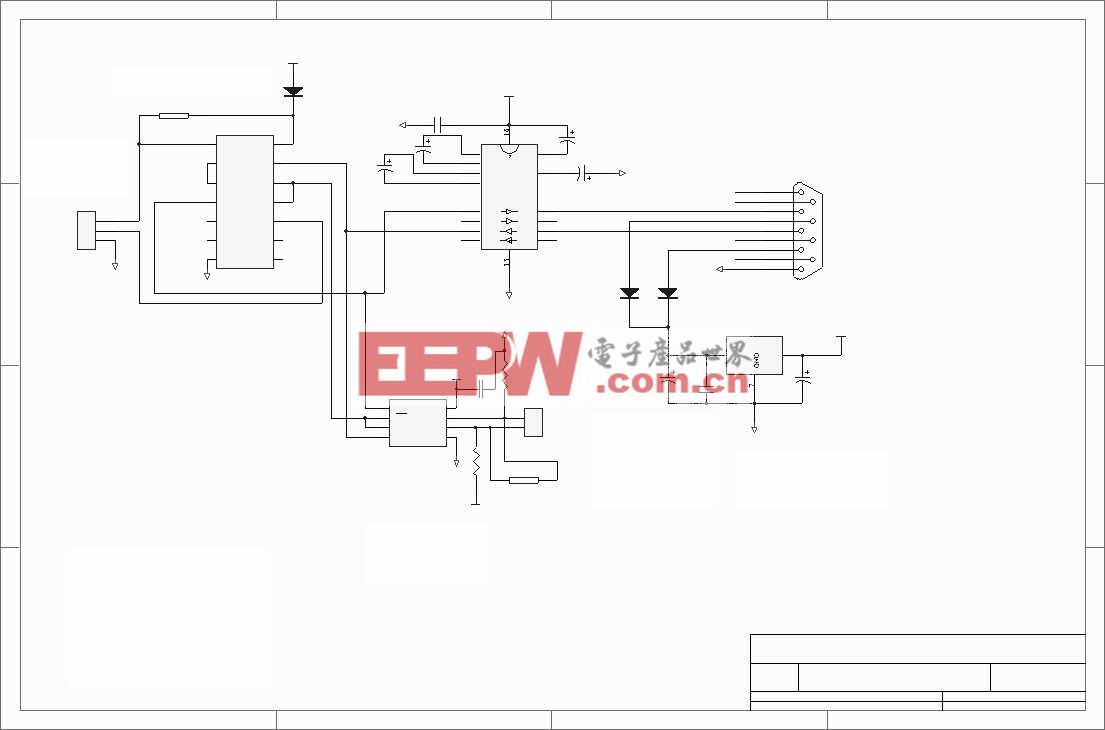

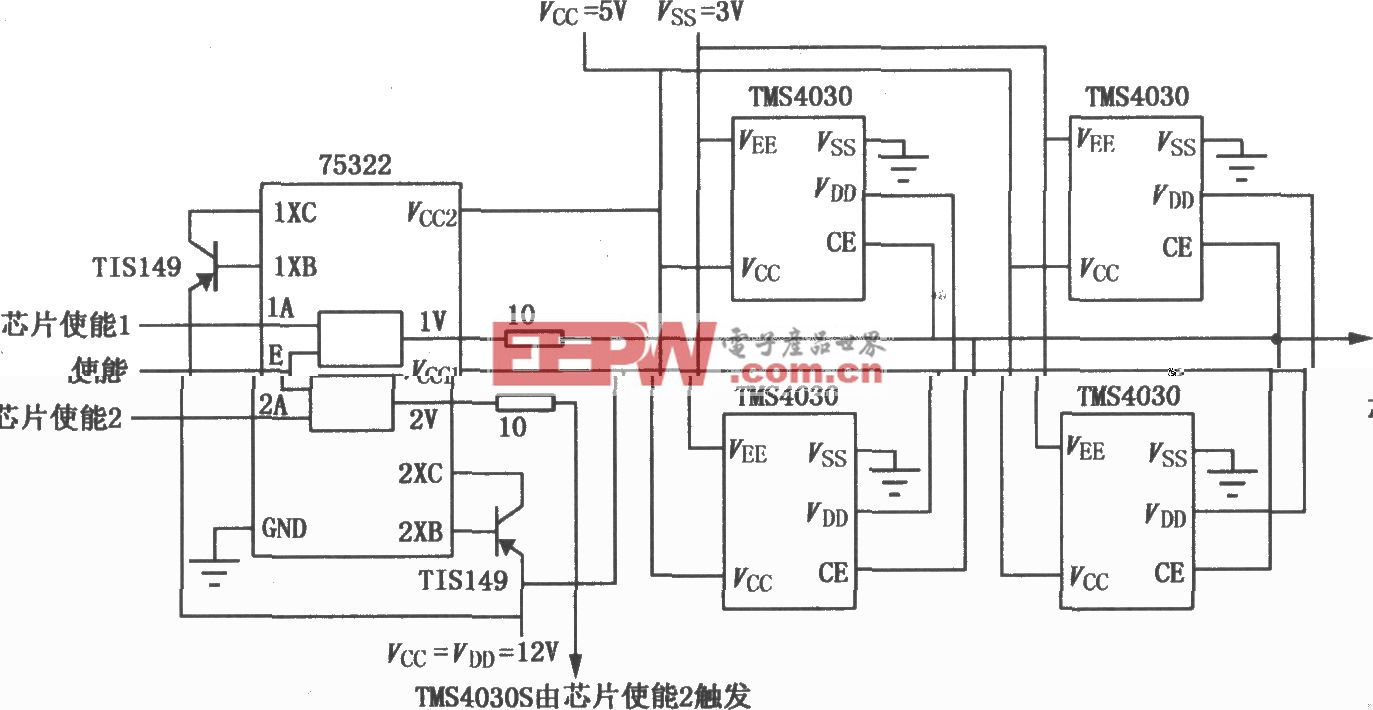

圖3 典型的TTL中速與非門電路

評論