高速低功耗FPGA的應(yīng)用設(shè)計(jì)

Actel公司是眾多FPGA生產(chǎn)廠家中的著名供應(yīng)商,美國(guó)的火星探路者使用了該公司的FPGA,表明它具有優(yōu)異性能。

本文引用地址:http://www.104case.com/article/3046.htm54SX系列FPGA是公司新一代產(chǎn)品,采用Actel專利的反熔絲技術(shù)制成。SX系列器件采用FastConnect與DirectConnect兩種創(chuàng)新的局部連線資源將邏輯塊連接在一起。一方面,這兩種連線為分段式連線資源,因而連接電容更小。分段結(jié)構(gòu)還允許切斷未使用連線,進(jìn)一步減小電容,連接電容的減小意味著功耗的降低;另一方面,該系列器件是在細(xì)顆粒的4輸入多路選擇器基本邏輯塊上構(gòu)建的,并且具備有多個(gè)控制輸入,一個(gè)基本單元能實(shí)現(xiàn)所有5輸入邏輯功能,使大規(guī)模的邏輯映射更有效。這種細(xì)顆粒結(jié)構(gòu)與大量分段式連線資源的結(jié)合,有助于在不降低性能的前提下減小功耗。

與其它FPGA廠家的產(chǎn)品相比,54SX系列器件還具有以下優(yōu)勢(shì):

* 可靠性高:芯片內(nèi)部采用金屬-金屬反熔絲元件,編程后內(nèi)部連接為永久的反熔絲型連接,而反熔絲互連就象純金屬連接一樣,防靜電及電磁干擾;

* 功耗低:反熔絲結(jié)構(gòu)消除了靜態(tài)存儲(chǔ)器互連開關(guān)的功耗,并且由于邏輯信息是永久性編程的,器件在通電序列中無(wú)需進(jìn)行重構(gòu),信息的存儲(chǔ)與保持不消耗電流,從而減小靜態(tài)電流,降低功耗;

* 保密性好:采用多層邏輯單元,內(nèi)部邏輯易破解。

以Actel FPGA實(shí)現(xiàn)的數(shù)字邏輯電路設(shè)計(jì),必須采用先進(jìn)的EDA(電子設(shè)計(jì)自動(dòng)化)軟件,該類軟件一般包括兩部分:邏輯電路設(shè)計(jì)部分和FPGA布局布線器。本文邏輯電路設(shè)計(jì)工具主要采用的是ViewLogic公司(已更名為Innoveda公司——編者注)的WorkView Office軟件包和Actel公司的邏輯功能模塊產(chǎn)生器Actgen Macro Builder。布局布線器是Actel公司的Designer軟件。

WorkView Office軟件包集成了多種數(shù)字電路計(jì)算機(jī)輔助設(shè)計(jì)工具,包括電路原理圖輸入軟件ViewDraw、VHDL(超高速集成電路硬件設(shè)計(jì)描述語(yǔ)言)、仿真軟件SpeedWave、VHDL綜合工具FPGA Express、門級(jí)電路仿真工具ViewSim、信號(hào)波形與時(shí)序顯示工具ViewWaves、邏輯設(shè)計(jì)結(jié)果與FPGA布局布線器接口軟件EDIF Interface等幾部分。

Actgen Macro Builder主要功能是生成基于Actel元件庫(kù)的可參數(shù)化的常用邏輯模塊,例如,計(jì)數(shù)器、寄存器、加法器、比較器等等。這些功能模塊可在ViewDraw中實(shí)例化,作為更上層功能單元的子模塊使用。Designer軟件包括EDIF編譯、工藝映射、設(shè)計(jì)優(yōu)化、延時(shí)約束、FPGA引腳指定、自動(dòng)布局布線、延時(shí)分析、延時(shí)信息反標(biāo)注、邏輯信息固化文件生成等多種功能。

為提高FPGA的數(shù)據(jù)處理速度及降低芯片功耗,邏輯電路設(shè)計(jì)應(yīng)重點(diǎn)采用以下措施:

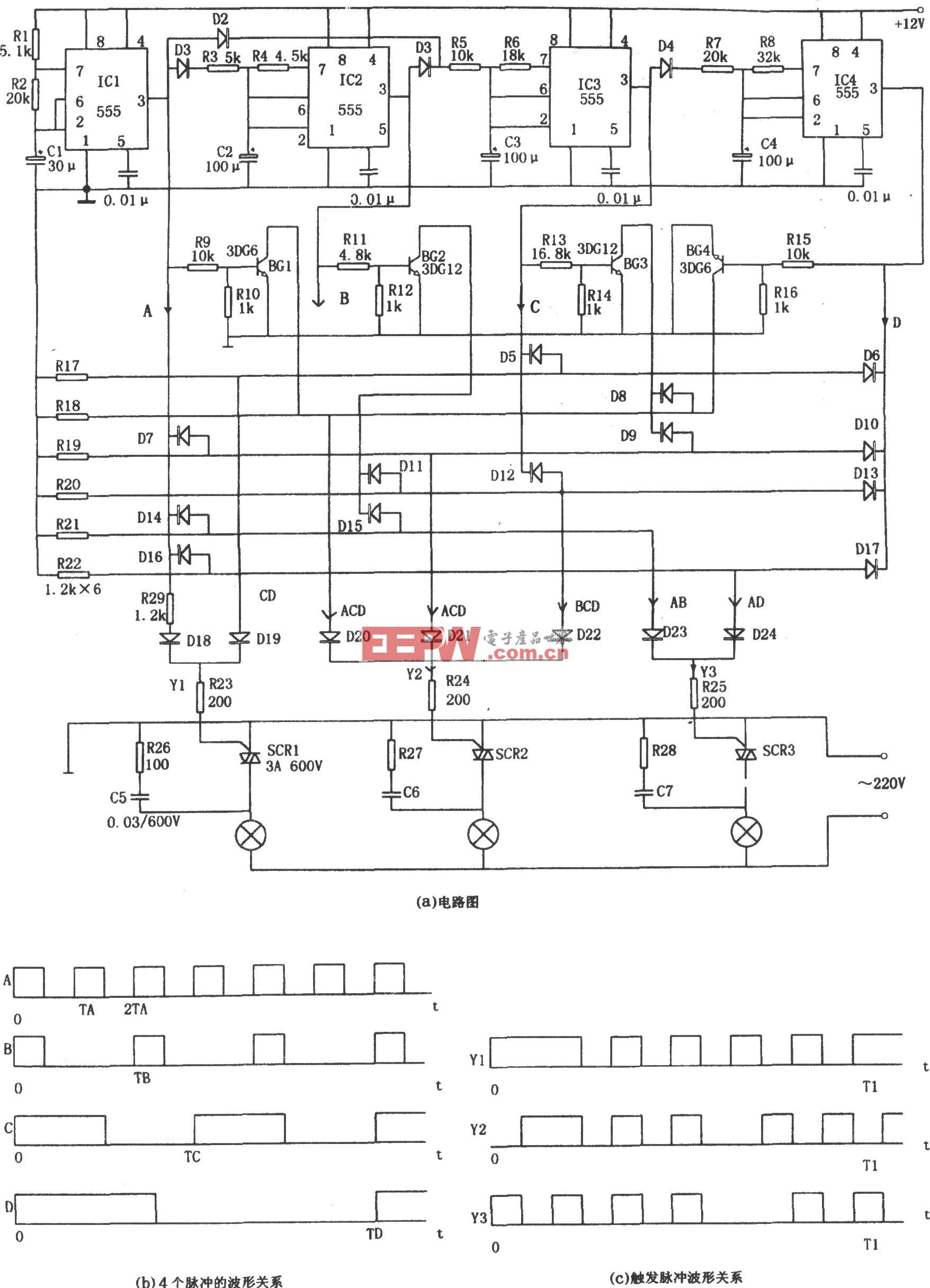

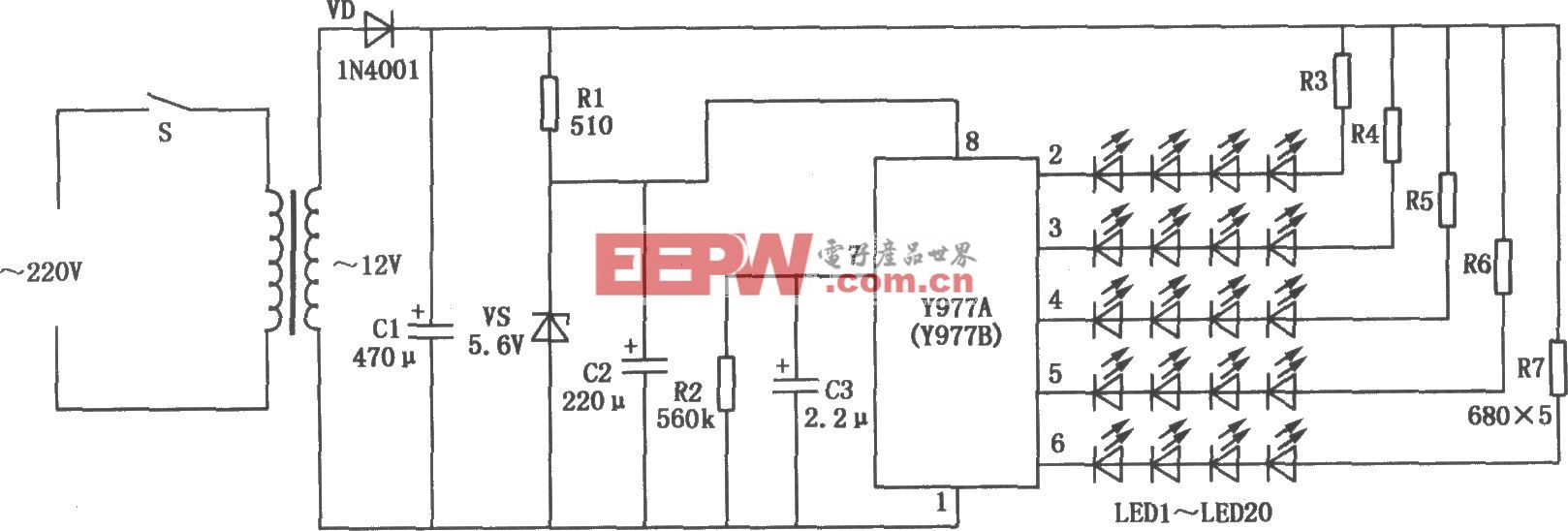

1)采用流水線,降低芯片功耗,提高系統(tǒng)時(shí)鐘。流水線是一種設(shè)計(jì)技巧,它在很長(zhǎng)的組合邏輯路徑中插入寄存器,寄存器雖增加了運(yùn)算周期數(shù),卻能大大減少組合邏輯延時(shí),提高整個(gè)系統(tǒng)工作頻率。例如,在如下計(jì)算模型Err=a-b-c+d中,沒(méi)有流水線的電路如圖1(a),引入流水線后,電路如圖1(b)。

為考察圖1a與圖1b兩種電路的速度差別,本文進(jìn)行如下實(shí)驗(yàn):

實(shí)驗(yàn)1:設(shè)計(jì)兩套數(shù)字電路A、B,并分別以兩片FPGA54SX32PQ208來(lái)實(shí)現(xiàn),其中電路A與圖1a無(wú)流水線電路對(duì)應(yīng),電路B與圖1b有流水線電路對(duì)應(yīng),電路A、B都使用具有超前進(jìn)位功能的16位快速加法器和減法器。仿真結(jié)果如表1中A,B所示。

結(jié)論:有流水線電路B在占用資源略有增加情況下,工作速度是沒(méi)有流水線電路A的2倍多,可見,少量資源換來(lái)了芯片工作速度的成倍增加。

2)按面積優(yōu)化組合邏輯,減小組合邏輯的復(fù)雜性,從而減少組合電路需要的邏輯門數(shù)量,邏輯門數(shù)的減少,意味著芯片功耗的降低。流水線的使用已經(jīng)保證芯片具有足夠高的處理速度,各個(gè)寄存器間的組合邏輯不再以速度為優(yōu)化目標(biāo)進(jìn)行設(shè)計(jì),考慮到功耗要求,應(yīng)以最少的邏輯門數(shù)實(shí)現(xiàn)該功能。例如,上面預(yù)測(cè)誤差的計(jì)算電路,其中加法器、減法器都使用簡(jiǎn)單的結(jié)構(gòu)形式,而不再使用超前進(jìn)位或更復(fù)雜的結(jié)構(gòu),這樣可以在節(jié)省邏輯門數(shù)情況下,電路仍具有高的處理速度,實(shí)驗(yàn)結(jié)果如表1。

實(shí)驗(yàn)2:使用結(jié)構(gòu)簡(jiǎn)單的加法器、減法器流水線電路C與電路A、B的比較實(shí)驗(yàn)。電路C采用流水線結(jié)構(gòu),使用的加法器、減法器也是16位,但結(jié)構(gòu)比電路A、B中的加法器、減法器簡(jiǎn)單,該電路在一片FPGA54SX32PQ208內(nèi)實(shí)現(xiàn)。仿真結(jié)果如表1的C所示。

結(jié)論:同電路A相比,電路C在資源節(jié)省13%條件下,工作頻率高出電路A 15%,達(dá)到45MHz以上;與電路B相比,電路C節(jié)省資源20%以上,并且由于45MHz的工作頻率對(duì)于復(fù)雜功能芯片(例如圖像或視頻編解碼芯片)來(lái)講,已經(jīng)足夠了。由此可見:在使用流水線的情況下,應(yīng)以邏輯門數(shù)為優(yōu)化目標(biāo),設(shè)計(jì)組合邏輯電路。

3)以原理圖描述功能模塊的數(shù)據(jù)流,以VHDL語(yǔ)言的行為語(yǔ)句描述控制流。這種邏輯電路設(shè)計(jì)思想,充分利用原理圖設(shè)計(jì)直觀、形象和VHDL輸入法簡(jiǎn)單明了的優(yōu)勢(shì),既可以獲得具有高效率流水線結(jié)構(gòu)的同步電路,又能夠大大縮短設(shè)計(jì)時(shí)間。

4)在電路設(shè)計(jì)過(guò)程中,應(yīng)使用“自底向上”與“自頂向下”設(shè)計(jì)相結(jié)合、“邏輯設(shè)計(jì)”與“功能仿真”交替進(jìn)行的設(shè)計(jì)技巧,以保證邏輯電路的層次化、模塊化以及功能的正確性。首先把邏輯復(fù)雜的功能模塊,分割為幾個(gè)相對(duì)簡(jiǎn)單的小模塊;然后分別設(shè)計(jì)這些小模塊,進(jìn)行功能仿真,發(fā)現(xiàn)錯(cuò)誤,修改設(shè)計(jì),再仿真……,直到功能完全正確;再實(shí)例化小模塊,組成功能復(fù)雜的大模塊,依舊重復(fù)功能仿真、修改設(shè)計(jì)的過(guò)程;再實(shí)例化這些大模塊,構(gòu)成更上層模塊……,最后獲得功能完全正確的邏輯電路。

如果邏輯電路不可能在單個(gè)芯片上實(shí)現(xiàn),必須對(duì)原有邏輯電路進(jìn)行功能拆分,分割為若干功能塊,每個(gè)功能塊在一片F(xiàn)PGA中實(shí)現(xiàn),整個(gè)電路由一組芯片實(shí)現(xiàn)。

電路拆分是一項(xiàng)具有試湊特點(diǎn)的工作,但還是有一定規(guī)律可以遵循:

1) 按照VLSI結(jié)構(gòu)設(shè)計(jì)時(shí)形成的功能模塊分割邏輯電路,同一功能模塊中的邏輯電路在一片F(xiàn)PGA中實(shí)現(xiàn),這樣保證了系統(tǒng)設(shè)計(jì)時(shí)的模塊化,便于設(shè)計(jì)的再利用、修改與升級(jí)。

2) 邏輯分割沒(méi)有必要平均化,而是考慮模塊功能的相對(duì)獨(dú)立性與模塊間的數(shù)據(jù)交換量,功能模塊間數(shù)據(jù)交換鏈路多的邏輯電路在一片F(xiàn)PGA內(nèi)實(shí)現(xiàn),這樣可以減少芯片的I/O引腳,降低功耗。

3)如果使用了片外存儲(chǔ)器,功能分割要使FPGA芯片組與存儲(chǔ)器之間的連接關(guān)系簡(jiǎn)單,有利于PCB布局布線。

邏輯電路設(shè)計(jì)完成,按以下步驟在FPGA中物理實(shí)現(xiàn):

1)、生成EDIF文件:使用 EDIF Interface工具將原理圖轉(zhuǎn)化成EDIF文件。

2)、編譯:使用Designer軟件編譯該EDIF文件,并指定FPGA器件為54SX系列。

3)、引腳定義:按照有利于印刷線路板設(shè)計(jì)的原則,定義FPGA引腳功能。

4)、布局布線:?jiǎn)?dòng)FPGA自動(dòng)布局布線器。

5)、延時(shí)分析:布局布線完成后,利用Designer軟件進(jìn)行分析,從中得到芯片的最高工作頻率。

6)、延時(shí)仿真:提取布局布線后的延時(shí)信息,進(jìn)行延時(shí)仿真。

7)、生成邏輯信息固化文件:延時(shí)仿真通過(guò)后,由Designer生成邏輯信息固化文件。

8)、制造芯片:使用特定編程器根據(jù)邏輯信息固化到FPGA中,從而制成專用芯片。■

參考文獻(xiàn)

Actel公司,Actel FPGA Data Book,2000.

評(píng)論