網絡處理器Intel IXP1200應用

隨著網絡規模和接口速度的增加,基于通用RISC技術的網絡設備無法在性能上滿足線速處理要求;另一方面新的網絡通信協議、標準不斷出現或變化,用戶的需求也在不斷變化之中,使得數據通信產品的更新換代周期迅速縮短。在這種背景下,網絡處理器(Network Processor,NP)為下一代通信產品的設計提供了一種靈活的解決方案。

本文引用地址:http://www.104case.com/article/3003.htm網絡處理器是一種專用于網絡通信設備的通用芯片,是一種開放式的、多樣化、可編程的開發環境,允許不同的設備供應商采用同樣的芯片制造出各自不同功能和特色的網絡設備。網絡處理器芯片專門針對通信功能進行了優化,綜合了RISC芯片和ASIC的優點——既像RISC可以軟件編程、提供足夠的靈活性來適應數據通信市場高速的發展,又具有ASIC那樣的高性能,但又不象ASIC那樣需要長達12個月的開發周期。通過下載不同的程序,同樣的硬件平臺可以支持Vlan交換機、路由器、寬帶接入服務器、NAT、防火墻、WEB交換機等,支持各種速率的以太網、ATM、POS等接口,升級非常方便。

目前提供NP的主要廠商有Agere、Intel、IBM、Maker/Conexant、MMC、Motorola等。IXP1200網絡處理器是Level-One公司(現屬Intel)的拳頭產品。

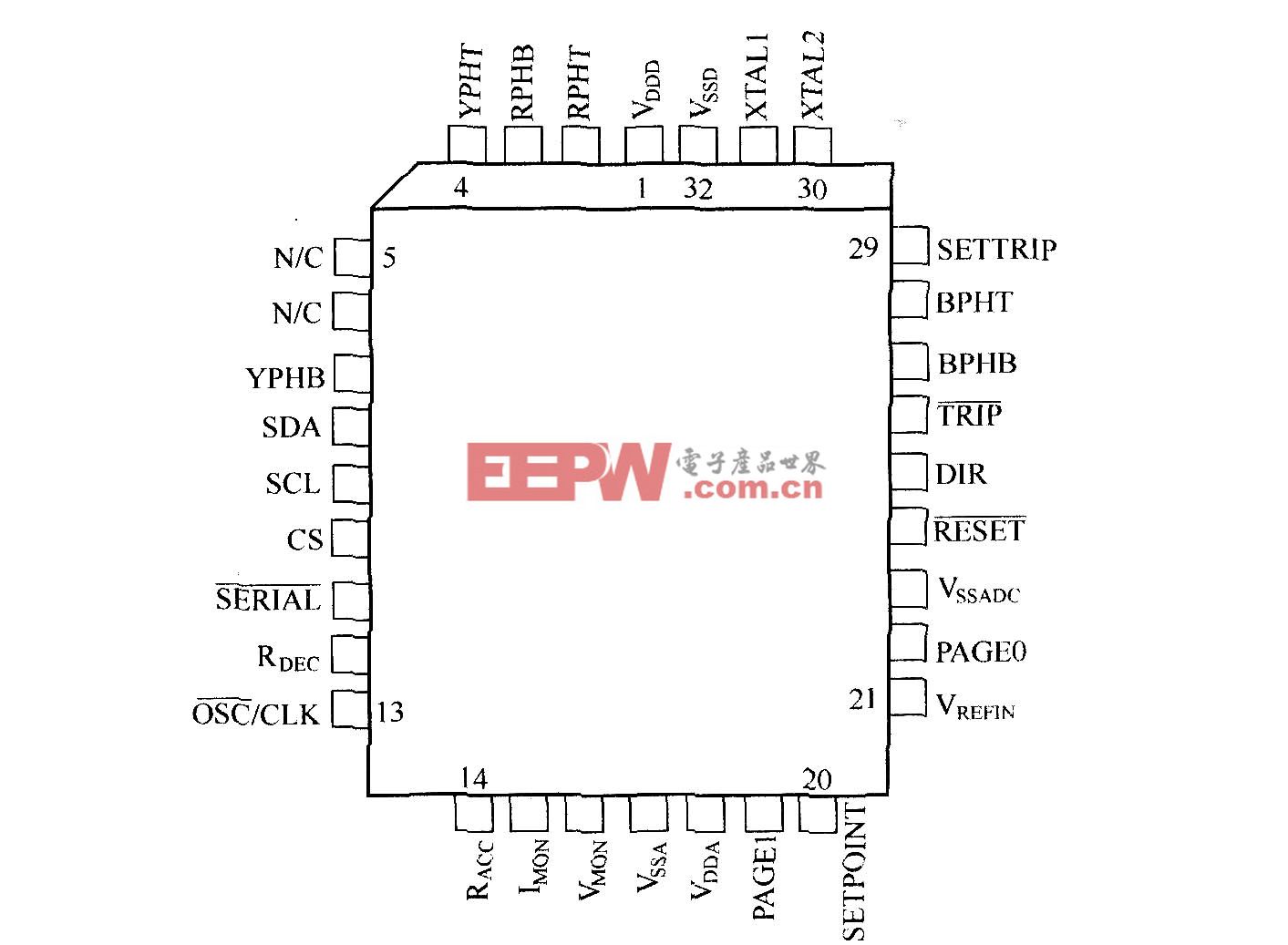

IXP1200由7個RISC處理器、外部存儲器接口、IX總線接口以及PCI總線接口等封裝于1個芯片上構成。7個RISC處理器當中有6個為包作業處理引擎以及1個管理/控制包作業處理引擎的“StrongARM”核。圖1為IXP1200結構圖。

IXP1200主要包括以下組件:

1.6個集成的32位可編程微引擎,工作頻率可達200MHz,每個引擎可支持四個線程,每個線程有獨立的程序計數器;

2.集成有Intel StrongARM 32位處理器(RISC)核,16K指令緩沖,8K數據緩沖,512字節的一次性臨時數據緩沖,寫緩沖,內存管理單元;

3.高帶寬4.2Gb/s 的I/O總線;

4.集成的32位,66MHz PCI總線接口。

網絡處理器的最大特點是可編程性,因此開發重點由硬件轉向軟件。IXP1200平臺上的軟件按運行位置可分為兩部分:StrongARM核上運行BSP、驅動程序、實時操作系統、路由表維護及上層應用程序,使用標準C語言開發;微引擎進行數據流輸入/輸出、打包/拆包、分類、快速查表、轉發等實時要求非常苛刻的處理。每個微引擎包含一段可編程的控制存儲器區(1024×32bit,1K條指令),用以存儲微碼程序。微引擎中的四個線程共享該控制存儲器。微引擎編程使用一套專為網絡數據流處理應用定制的指令集,去掉了通用RISC芯片中對協議及包處理用處不大的部分,同時保留了RISC指令長度一致、單周期執行時間、易于并行和流水線處理等優點。

微引擎目前可以使用33條基本指令,大部分指令可以有不同執行選項,合理組合使用可以達到最高性能。指令集合按功能可以分為如下五類:算術邏輯運算、移位類;分支及跳轉類;訪問類指令;本地寄存器操作;雜類指令。

Intel鼓勵使用宏風格的編程方式,提供了一套宏庫,大大提高了編程效率及軟件可維護性。

IXP1200是通過硬件和軟件的并行開發來縮短開發周期的。Intel免費提供了一個完全集成的開發環境Developer Workbench用于微碼編程、符號匯編、鏈接、仿真、調試、性能分析等,使用界面類似微軟的Visual C++。一個完整的工程包括:工程文件、微碼源程序文件、宏庫、調試腳本、生成映象文件的匯編及鏈接設置、仿真外圍器件或ARM應用程序的外部DLL等。相比常見的集成開發環境,其仿真模擬器和擴展外部模塊比較有特色。

IXP1200編程最大的挑戰在于利用其微引擎硬件多線程處理特性,充分利用現有存儲器帶寬,從而滿足高速處理要求。設計者需要折衷考慮硬件高速處理和軟件靈活性,主要圍繞優化數據處理性能,包括數據包分類、指令效率、數據管理、控制通道和數據通道隔離、查表加速,還有存儲器容量和可擴展性等方面。下面總結一些提高處理性能的經驗。

1、程序結構組織及線程資源的合理分配使用;根據具體應用處理要求,在設計中可以將線程分為接收調度、接收、發送調度、發送、包處理等線程。各個微引擎進行相應的分工,使其協同工作,性能最優,同時使各個階段的處理相對獨立,功能模塊化,程序結構清晰。

2、不同內存資源的靈活使用:SRAM讀寫速度快,但價格高配置容量小,一般用于使用頻繁的索引表、隊列等;SDRAM容量大,主要作為包緩沖區、大的復雜數據區;SCRATCH暫存區作為片內小容量的存儲區。

3、靈活運用指令選項進行優化:微碼指令通常按五級流水線方式執行,當執行管道被指令填滿時,則每個指令周期都將有一條指令完成,但分支指令、跳轉指令、上下文切換指令等會引起執行管道中的指令異常退出,從而導致微引擎效率降低。解決方法是巧妙安排指令執行順序,使用優化選項。

后延分支(Defer)的目的在于減少或消除執行管道中的異常退出指令。在后延分支中,緊跟在分支決定后的指令可以在分支生效前執行。如果在分支指令后可找到有用的工作來填充浪費的指令周期,則分支引起的等待時間就可隱藏起來。

猜測分支(Guess Branch)可選標識允許在實際的分支決定作出之前,從分支路徑上預取指令。因此為使程序管道指令運行效率更高,在編程中應注意分支指令周圍的指令安排:適當使用deferred branch,在分支指令后面安排一些指令以填充指令執行管道;用于分支決定的條件代碼應盡早確定;根據處理器的猜測分支邏輯安排分支語句,并適當地加上分支可選標識。

在讀寫SRAM、SDRAM類指令后可用ctx_swap選項,使得訪問存儲器的延時可以被其它線程利用。同樣在一段較長的處理過程中加入ctx_arb[voluntary]讓其它線程有機會運行。

4、盡可能使用高效率的算法:

微引擎包處理很大一部分工作(如路由查找、過濾匹配)需要進行各種查表處理,采用高效的查找算法可以提高處理性能。如使用IXP1200硬件HASH功能一次可以計算出三個鍵值,多項式HASH算法中用到的乘子多項式值可以根據分布特點選取以得到最佳的HASH結果,減少沖突概率。■

參考文獻

1 IXP1200 Network Processor Datasheet

2 IXP1200 Network Processor Hardware Reference Manual

3 IXP1200 Network Processor Programmer's Reference

4 IXP1200 Network Processor Software Reference Manual

c++相關文章:c++教程

評論