Altera Stratix 10 DRAM SIP突破帶寬瓶頸

計劃于2017年出貨的最新的Stratix 10 DRAM SiP產品將采用存儲器廠商現代公司的HBM DRAM內存,通過英特爾先進的嵌入式多裸片互連橋接(EMIB)技術,將FPGA、MCU、DSP以及DRAM等其他功能模塊集成在2.5D的SiP封裝內,實現一個異構多核的SoC FPGA產品。相對于目前的分立DRAM解決方案,Stratix 10 DRAM SiP的存儲器帶寬提高了10倍。

本文引用地址:http://www.104case.com/article/283392.htm伴隨著客戶對系統的要求不斷攀升,處理器芯片的技術不斷地提升性能,隨著技術難度增加,發展將越來越慢。而FPGA方面,還有EMIB的技術、存儲技術等,不管是DDR3、DDR4,它們已經不再能夠跟上客戶對系統的要求了,所以關鍵就是在存儲器帶寬上。但存儲器子系統所提供的帶寬與系統要求的存儲器帶寬差距越來越大。

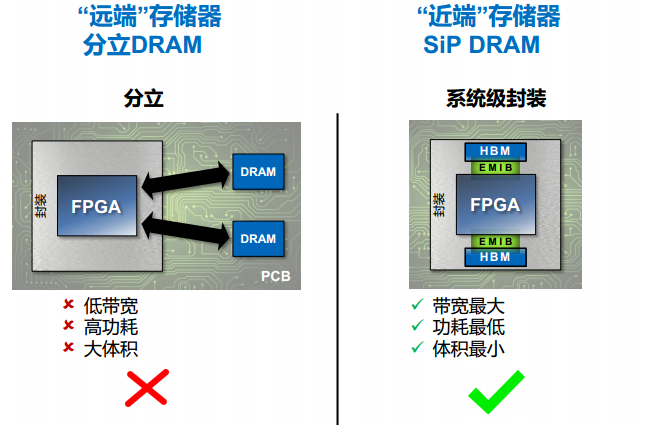

如圖1所示,傳統的“遠端”存儲器分立DRAM由于其低帶寬、高功耗、大體積不能滿足下一代應用的需求。Altera Stratix 10 DRAM SIP 產品本身的電路板它的尺寸變小,DRAM器件直接被集成到了FPGA的器件里面,因此就出現了所謂原來的傳統的遠端的存儲器變成了近端的存儲器。這樣做有三大優勢,第一可以實現最大的帶寬,10倍于以前的帶寬;第二體積最小,可以把更多的管芯放到一個單一的封裝中;第三它的功耗可以實現最低。 圖1 DRAM SIP與傳統DRAM 對比

據了解,Stratix 10系列面向的包括數據中心、HPC、雷達、定制服務器等高端市場。通過英特爾獨有的EMIB技術實現,相對于現在流行的TSV技術連起來的話,在信號的完整性和性能、功耗等方面都具有優勢。

Altera公司高級產品營銷總監 Manish Deo對此解釋道:“EMIB的技術其實強調是系統級的這樣一個互聯集成的技術,當你需要把FPGA和外部世界,其實就是外部器件系統相連的時候,任何一個技術廠商都是要盡量多地避免使用TSV,因為如果你要用TSV連接的話,意味著你的信號,也就是數據要不斷地推動TSV進出,而事實上我們任何一個系統,尤其是高處理的這些系統解決方案都有大量的數據的進出,所以吞吐量是非常之大的,EMIB的好處就是當FPGA和外界系統相連接的時候,它可以完全繞過TSV,不再需要通過TSV去訪問存儲器。所以這是EMIB的技術和任何其他的基于中介質集成的解決方案根本上的不同。”

Altera公司產品營銷資深總監Patrick Dorsey在其最新產品Stratix 10 DRAM SiP的發布會表示:“SoC FPGA已經進入4核乃至16核時代,集成有500多萬個邏輯單元,DSP的浮點運算能力達到10T FLOPS,面臨的一個關鍵的問題是這些數據如何快速傳輸到核心處理單元, 因此存儲器的訪問越顯重要。

評論