緩沖器反饋路徑中的電阻器:問問為什么!

每當檢查年輕工程師的電路原理圖或印刷電路板 (PCB) 布局布線時,我都要挑選幾個項目,問他們“為什么這么做?”為什么你選擇這個組件?為什么把它布置在 PCB 的這個位置?之所以問這些問題是因為工程師在做出每個設計決策時都應該有合理的理由。

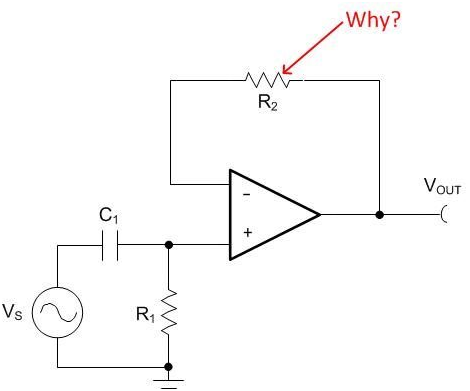

本文引用地址:http://www.104case.com/article/282925.htm例如,在配置成緩沖器的運算放大器反饋路徑中有一個電阻器,應該馬上想到“這是為什么呢?”

令人難以接受的實際情況是工程師經常不知道自己為什么使用電阻器 R2。他們可能在以前的原理圖中看到過,所以感到必須包含這個電阻器。這些電阻器通常用于低速應用 (<50 MHz),以消除運算放大器輸入偏置電流產生的 DC偏移。

R2 還可能會在輸出出現 靜電放電 (ESD) 沖擊時為反相輸入提供一定的保護。此外,如果兩個輸入端有匹配的電源阻抗,有些運算放大器(特別是 JFET 輸入型)就會產生較低的失真。但如果不理解 R2 的用途,通常就會隨機選擇該值,從而導致不穩定性。

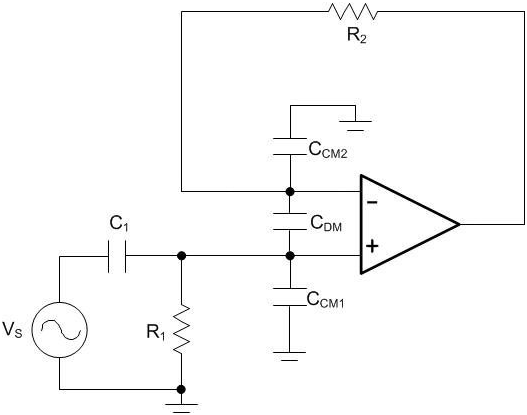

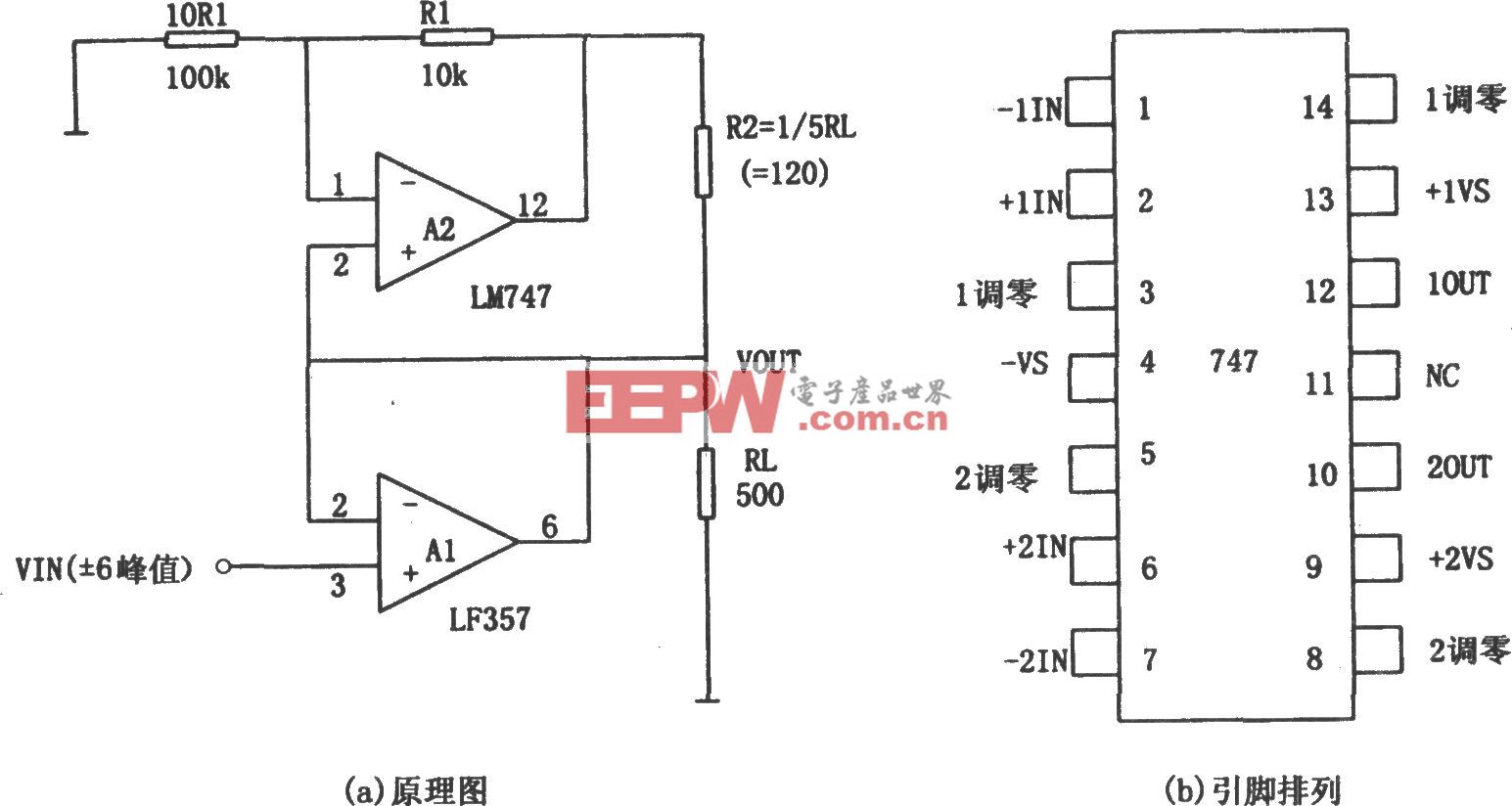

要理解 R2 導致不穩定性的原因,我們在該電路中加入運算放大器的輸入電容,如圖 2 所示。

圖 2:在圖 1 電路中加入運算放大器輸入電容

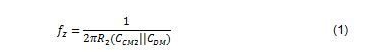

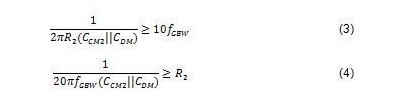

R2 與輸入共模電容 CCM2及輸入差分電容 CDM在反相輸入端構成一個低通濾波器。反饋路徑中的低通濾波器在放大器的噪聲增益曲線 (1/β) 上產生一個零值,所處頻率為:

如果該零值遠遠高于放大器的單位增益帶寬,如圖 3 中fz(2)所示,它就不會影響電路的穩定性。但如果這個零處于或低于運算放大器的單位增益帶寬位置,例如fz(1),噪聲增益曲線就會以大于每十倍頻程 20dB 的速率與開環增益曲線相交,表明有可能產生的不穩定性。

圖 3:緩沖器放大器的開環增益(紅)和噪聲增益(藍)曲線

該零值的相移在低于fz的十倍頻位置開始,因此保守設計原則是:

用該公式替換fz,我們便可確定能確保穩定性的 R2最大值:

為了展示該效果,我對采用緩沖器配置的OPA172進行了仿真,并測量了不同 R2 值的相位裕量。OPA172的單位增益帶寬是 10MHz,輸入共模與差分電容均為 4pF。使用公式 4 中的設計準則,R2 的最大值是:

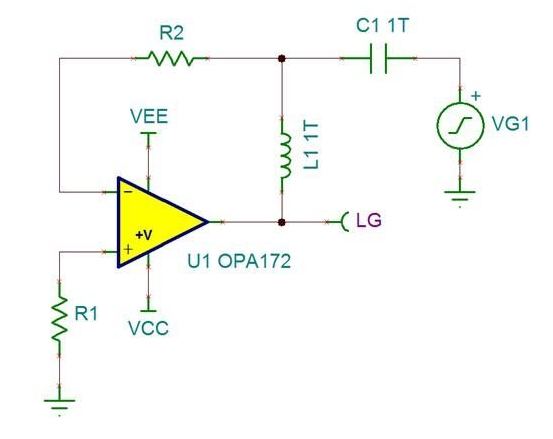

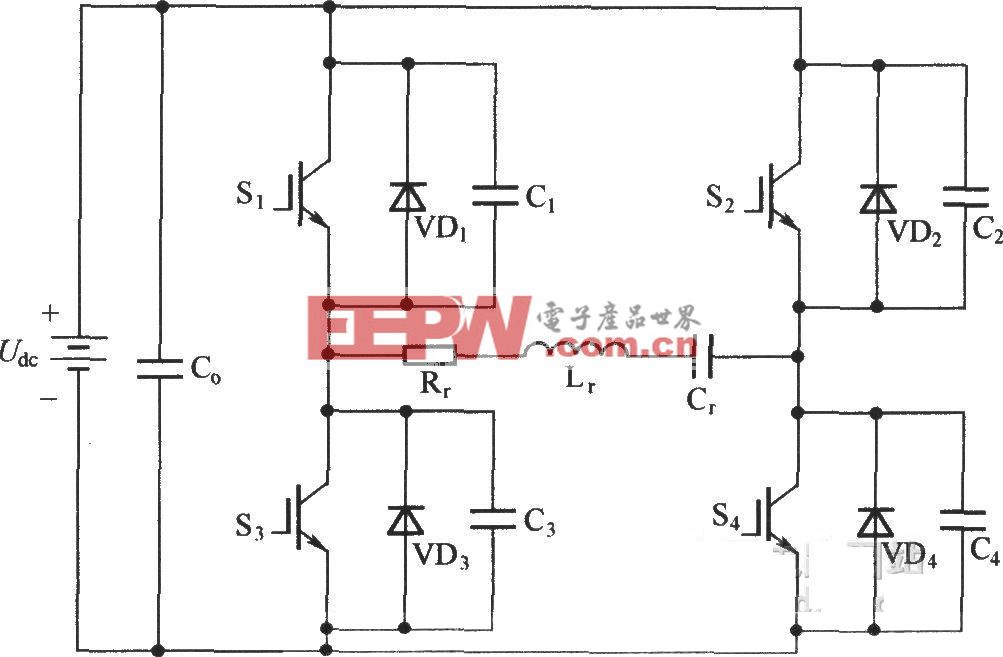

圖 4 是我用來測量相位裕量的TINA-TI?仿真電路原理圖。反饋環路在運算放大器輸出端由電感器 L1 損壞,一個電源 (VG1) AC 耦合至該反饋環路。環路增益由具有“LG”標識的探針提供,在環路增益等于 0dB 時,可測量相位裕量。

圖 4:配置為緩沖器的OPA172的TINA-TI?仿真電路原理圖

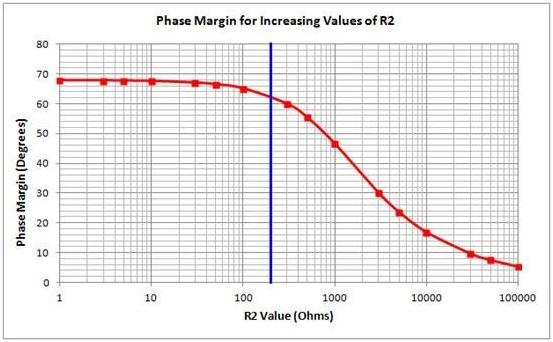

圖 5 是在 R2值增加時相位裕量的曲線。藍線是我們用公式 5 計算出的 R2 最大值。在低于該限值時,相位裕量的降低最小,在 R2 = 200 歐姆時僅降至 62°,而高于該限值時,相位裕量則會快速降低。

圖 5:OPA172相位裕量及 R2值的比較曲線

記住這一分析不包括電容負載或 PCB 寄生效應的影響,但它們也會降低電路的相位裕量。

在某些電路中可能會有使用 R2的適當理由,但在將其納入電路原理圖之前,要問問自己,使用該電阻器希望達到什么效果。如果所需的值很大,您可能會遇到穩定性問題。在任何工程設計工作中多問“為什么”,對工程師自我提高十分關鍵!

評論