CN0360:一個頻率可調射頻檢波器

常見變化

本文引用地址:http://www.104case.com/article/277973.htm用帶寬更寬的分立式鎖相環(PLL,如ADF4155或ADF4156)和外部VCO取代頻率合成器ADF4351,可將電路的頻率范圍擴展到6 GHz。 通過改變SAW濾波器,可以調整電路的中頻頻率、濾波器帶寬和插入損耗。 提高濾波器的帶寬和插入損耗會提高噪聲電平,從而降低系統的動態范圍。 混頻器、VGA和濾波器的積分輸出噪聲電平必須比RMS檢波器的標稱輸入靈敏度低6 dB到10 dB。 可利用ADIsimRF™來計算電路前端(混頻器、VGA和濾波器)的積分噪聲。 將該電路連接AD7091或AD7466等模數轉換器(ADC),可對電路輸出電壓進行數字化轉換。 更多信息參見電路筆記CN-0178。

電路評估與測試

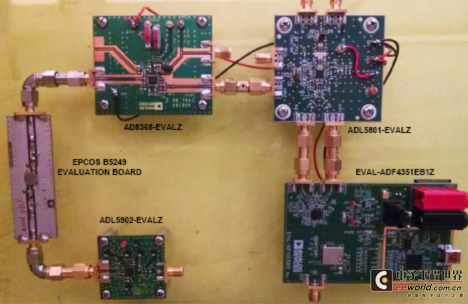

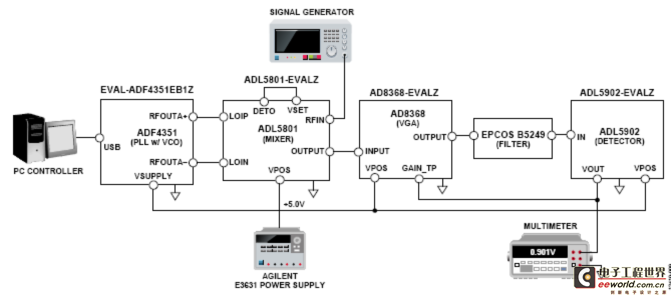

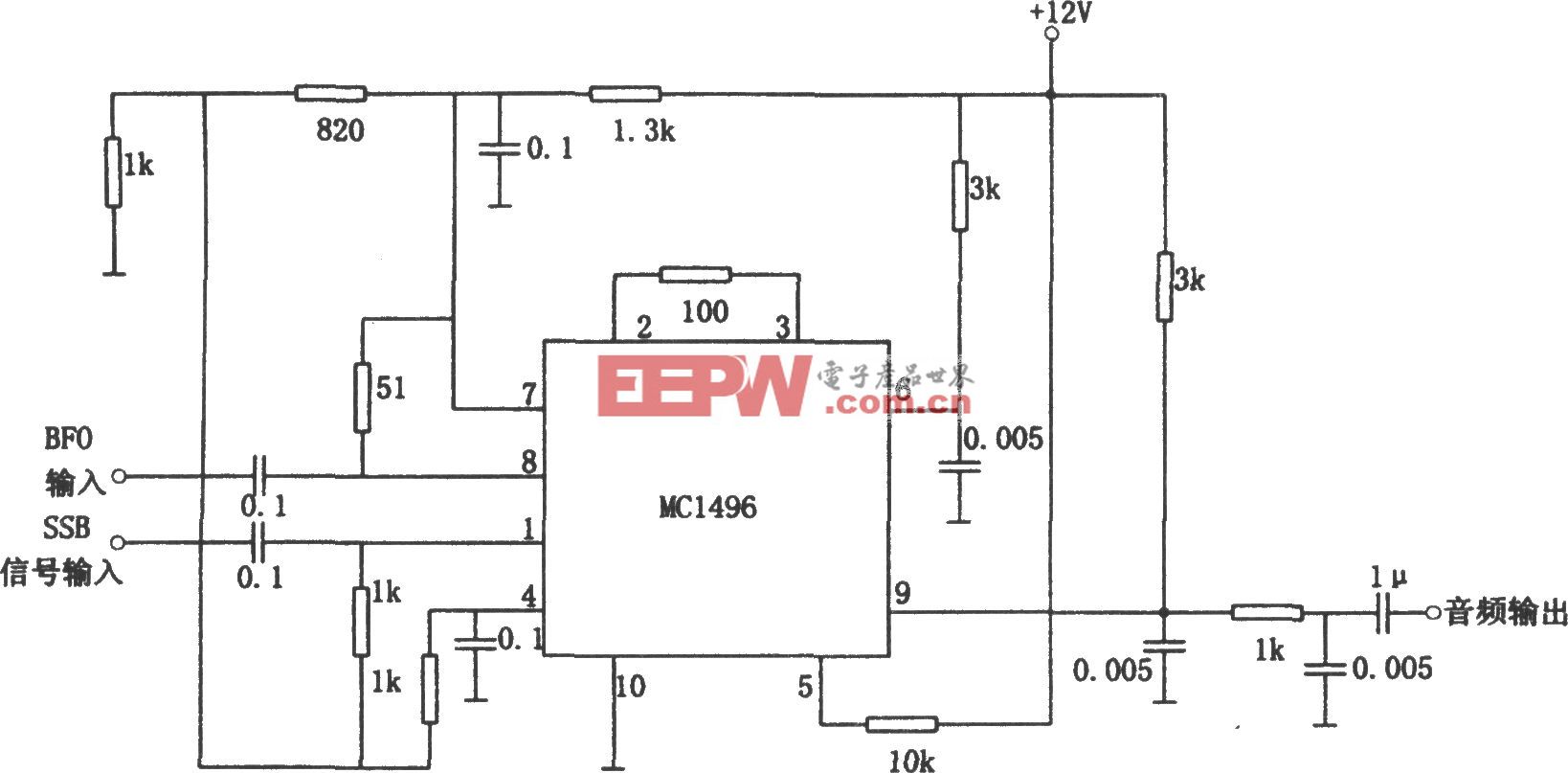

該電路利用ADL5902 (ADL5902-EVALZ)、AD8368 (AD8368-EVALZ)、ADF4351 (EVAL-ADF4351EB1Z)、ADL5801 (ADL5801-EVALZ)標準評估板及一個裝有EPCOS B5249 SAW濾波器的濾波器評估板實現。 由于全部評估板均提供50 Ω接口,因此它們通過桶形SMA連接器直接連接。 使用測試夾連接從ADL5902檢波器輸出回到AD8368增益控制輸入的信號連接,并連接VSET和DET0引腳以配置ADL5801的自適應偏置控 制。 縮小ADL5902檢波器輸出電壓所需的電阻分壓器是通過在ADL5902評估板的R1 (3.83 kΩ)和R15 (1.5 kΩ)焊盤上表貼安裝電阻來實現的。 在140 MHz時,優化電路溫度穩定性的TADJ電壓通過R9/R12電阻分壓器設置,該分壓器以2.3 V片上基準電壓源作為輸入。 若要將TADJ電壓設為推薦的0.6 V電平,可將R9改為850 Ω(R12保持現有值301 Ω)。

圖8所示為裝配完善的應用電路,圖9所示為測試設置的功能框圖。

圖8. 裝配完善的應用電路

圖9. 電路評估測試設置

設備要求

以下列出了用來評估電路的設備清單。

•帶USB端口的Windows® XP、Windows Vista(32位)或Windows 7(32位)PC

•ADL5902-EVALZ、AD8368-EVALZ、EVAL-ADF4351EB1Z和ADL5801-EVALZ評估板

•EPCOS B5249評估板

•一個RF信號發生器

•一個數字萬用表

•一個電源

利用ADF4351控制軟件設置將輸入信號下變頻至140 MHz中頻所需的LO頻率。 然后逐步提高輸入功率水平,并測量電路的RMS輸出電壓,從而確定電路的傳遞函數和誤差一致性曲線。

為測試電路對阻塞信號的抑制性能,使用一個信號發生器模擬阻塞信號,并利用主信號發生器模擬目標通道,用這兩個信號驅動電路。 然后逐步提高阻塞信號電平,觀測電路的響應,并評估電路性能。

CN-0360設計支持包:

CN-0239電路筆記,帶無縫本振接口的寬帶6 GHz有源混頻器,ADI公司。

CN-0340電路筆記,檢波范圍為95 dB的真RMS RF檢波器,ADI公司。

CN-0150電路筆記,經軟件校準的1 MHz至8 GHz、70 dB RF功率測量系統,ADI公司。

CN-0178電路筆記,經軟件校準的50 MHz至9 GHz RF功率測量系統,ADI公司。

ADIsimRF設計工具

ADIsimPLL™設計工具

UG-435用戶指南,ADF4351小數-N分頻PLL頻率合成器的評估板。

UG-476用戶指南,PLL軟件安裝指南。

MT-031指南,實現數據轉換器的接地并解開“AGND”和“DGND”的謎團,ADI公司。

混頻器相關文章:混頻器原理

評論