詳解JESD204B串行接口時(shí)鐘需求及其實(shí)現(xiàn)方法

隨著數(shù)模轉(zhuǎn)換器的轉(zhuǎn)換速率越來(lái)越高,JESD204B串行接口已經(jīng)越來(lái)越多地廣泛用在數(shù)模轉(zhuǎn)換器上,其對(duì)器件時(shí)鐘和同步時(shí)鐘之間的時(shí)序關(guān)系有著嚴(yán)格需求。本文就重點(diǎn)講解了JESD204B數(shù)模轉(zhuǎn)換器的時(shí)鐘規(guī)范,以及利用TI公司的芯片實(shí)現(xiàn)其時(shí)序要求。

本文引用地址:http://www.104case.com/article/270296.htm1. JESD204B介紹

1.1 JESD204B規(guī)范及其優(yōu)勢(shì)

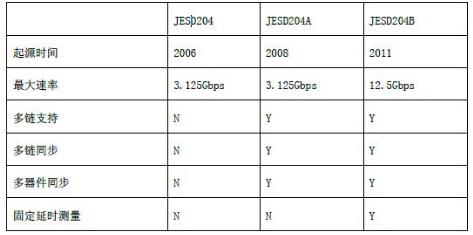

JESD204是基于SerDes($174.9800)的串行接口標(biāo)準(zhǔn),主要用于數(shù)模轉(zhuǎn)換器和邏輯器件之間的數(shù)據(jù)傳輸,其最早的版本是JESD204A,現(xiàn)在是JESD204Bsubclass0,subclass1,subclass2.區(qū)別主要在于其對(duì)同步和鏈路間固定時(shí)差的測(cè)量。目前市場(chǎng)上比較多地?cái)?shù)模轉(zhuǎn)換器接口是JESD204B subclass1.其最大傳輸速率可達(dá)12.5Gbps,支持多鏈路和多器件的同步以及固定時(shí)差的測(cè)量。下表是各版本之間的差異:

Table 1

在JESD204接口出現(xiàn)以前,數(shù)模轉(zhuǎn)換器的數(shù)字接口絕大多數(shù)是差分LVDS的接口,這就造成了布板的困難,當(dāng)PCB的密度很大的時(shí)候就需要增加板層從而造成印制板的成本上升。而JESD204B接口是串行接口,能有效減少數(shù)據(jù)輸出的差分對(duì),能最大限度的簡(jiǎn)化Layout.因此JESD204B是高密度板不可或缺的接口。但因其需要進(jìn)行嚴(yán)格的同步和以及時(shí)延的測(cè)量,與之接口的邏輯會(huì)比LVDS接口復(fù)雜很多,幸運(yùn)的是現(xiàn)在邏輯廠商都集成了專用的JESD204IPCore在他們的軟件里,從而簡(jiǎn)化了邏輯的設(shè)計(jì)。

1.2 JESD204B時(shí)鐘的需求

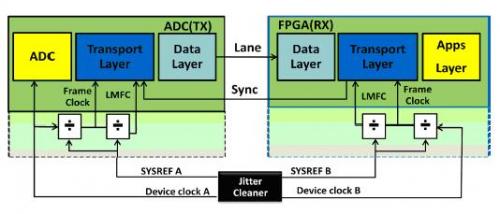

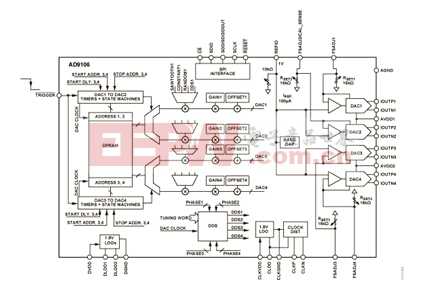

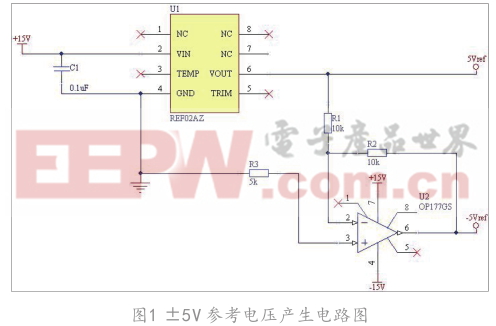

盡管JESD204B也有不同的版本,但越來(lái)越多的廠商選擇Subclass1,因此市面上絕大多數(shù)的數(shù)模轉(zhuǎn)換器都是基于這個(gè)版本設(shè)計(jì)的。本文就以JESD204B subclass1來(lái)討論時(shí)鐘的時(shí)序需要以及TI時(shí)鐘芯片方案的實(shí)現(xiàn)。任何一個(gè)串行協(xié)議都離不開幀和同步,JESD204B也不例外,也需要收發(fā)雙方有相同的幀結(jié)構(gòu),然后以一種方式來(lái)同步,即辨別起始。JESD204B是以時(shí)鐘信號(hào)的沿來(lái)辨別同步的開始,以及通過(guò)一定的握手信號(hào)使得收發(fā)雙方能夠正確識(shí)別幀的長(zhǎng)度和邊界,因此時(shí)鐘信號(hào)及其時(shí)序關(guān)系對(duì)于JESD204B就顯得極其重要。下圖是典型的JESD204B系統(tǒng)的系統(tǒng)連接,Device Clock是器件工作的主時(shí)鐘,一般在數(shù)模轉(zhuǎn)換器里為

圖1

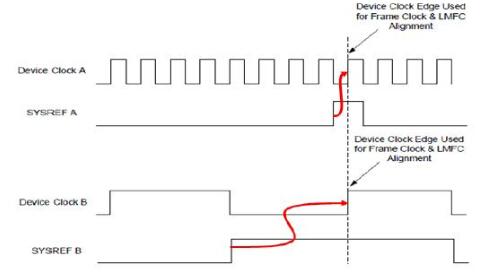

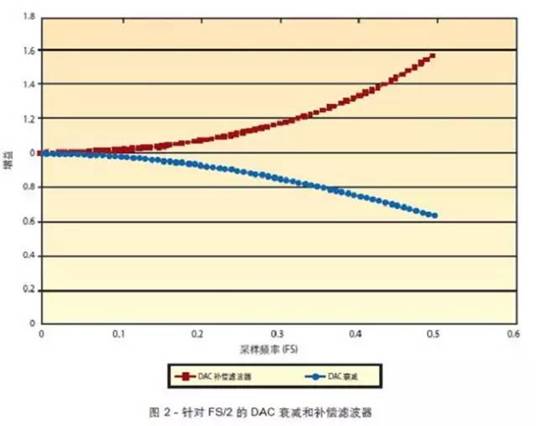

其采樣時(shí)鐘或者整數(shù)倍頻的時(shí)鐘,其協(xié)議本身的幀和多幀的時(shí)鐘也是基于Device Clock.SYSREF是用于指示不同轉(zhuǎn)換器或者邏輯的Device Clock的沿,或者不同器件間Deterministic latency的參考。如下圖所示,Device Clock和SYSREF必須滿足的時(shí)序關(guān)系。

圖2

SYSREF的第一個(gè)上升沿要非常容易的能被Device Clock捕捉到,這樣就需要SYSREF和Device Clock滿足上圖的時(shí)序關(guān)系。通常會(huì)因?yàn)镻CB的線長(zhǎng)以及時(shí)鐘器件不同通道輸出時(shí)的Skew,會(huì)帶來(lái)一定的誤差,Device Clock的上升沿不一定正好在SYSREF的脈沖的正中間,工程上只要在一定范圍內(nèi)就能保證JESD204收發(fā)正常工作。

評(píng)論