邏輯分析儀我也DIY(三)—PLL后復位問題

關于M4K的問題還沒有結束。主要問題在于想利用M4K來存儲要顯示到VGA屏幕上的字模數據,而昨天為了方便開了一個很大位寬的M4K,結果就照成了M4K的利用率大大下降,原來不到8K的數據居然占用了7個M4K塊,感覺不爽。所以今天絞盡腦汁是想出了解決辦法,同時也為其他字符的顯示方法開了綠燈。

本文引用地址:http://www.104case.com/article/269807.htm具體方法不在此討論,不過現在原來占用7個M4K的字模改成了32位寬*224,規規矩矩的占用了2個M4K塊。此外把常用的8*16的ASCII字符字模數據都存到了M4K初始化ROM里了,這全都是體力活,耗費了不少精力。主要問題是字模軟件和altera提供的標準ROM初始化文件的格式沒法搞成一致。400多個字數據都是手工編號,小指頭現在還隱隱作痛。不過顯示的技術難點解決了,感覺還是蠻開心的。

其次,對于采樣頻率(采樣周期)做了細化,不再是原來單一的只能為100MHz的采樣率,現在可以有10檔可調的采樣頻率。因為采樣率設置后的顯示還沒有繼續搞定,所以暫時不做進一步的測試。

因為這個工程里的兩個時鐘都是用的PLL產生的,所以有必要探討一下使用了PLL輸出時鐘作為系統工作時鐘時的復位邏輯設計。特權同學的一點愚見,愿拋磚引玉,期待高手指點。

以前的很多博文里都談過異步復位、同步釋放等等的問題,那么在系統復位后PLL時鐘輸出前,即系統工作時鐘不確定的情況下,怎么考慮這個復位的問題呢?

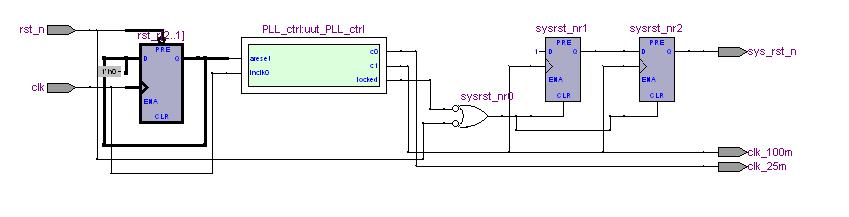

上圖是特權同學的這個工程里的復位設計,先用FPGA的外部輸入時鐘clk將FPGA的輸入復位信號rst_n異步復位、同步釋放處理一下,然后這個復位信號輸入PLL,同時clk也輸入PLL。我的設計初衷是在PLL輸出時鐘有效前,系統的其它部分都保持復位狀態。PLL的輸出locked信號在PLL有效輸出之前一直是低電平,PLL輸出穩定有效之后才會拉高該信號。所以這里就把前面提到的FPGA外部輸入復位信號rst_n和這個locked信號相與作為整個系統的復位信號,當然了,這個復位信號也是需要讓合適的PLL輸出時鐘異步復位、同步釋放處理一下。

評論