基于VIM的嵌入式存儲控制器的研究與實現

1 引言

本文引用地址:http://www.104case.com/article/265390.htm隨著VLSI技術的迅猛發展,微處理器主頻日益提高、性能飛速增長,盡管與此同時存儲器集成度也越來越高、存取延時也在不斷下降,但是處理器性能的年增長速度為50%~60%,而存儲器性能每年提高的幅度只有5%~7%,DRAM存儲器的低帶寬和高延遲使高性能處理器無法充分發揮其性能,處理器和存儲器之間速度的差距越來越成為制約整個系統性能的瓶頸。眾多的研究者從微體系結構出發,采取亂序執行、多線程、預取、分支預測、推斷執行等技術,或多級Cache的層次式存儲結構來彌補微處理器與存儲器性能差距,但是這些技術存在多種問題:復雜、占用面積大、資源利用率低、造價高、耗盡存儲帶寬等,并不能真正解決存儲瓶頸問題。即使一些新的存儲器產品的出現,如DDR存儲器,Rambus存儲器等,雖然一定程度上提高了存儲器的頻率,但處理器和存儲器之間的性能差距還是在進一步拉大。如何才能真正消除存儲器性能瓶頸呢?PIM技術(Processing in Memory),即把處理器和存儲器緊密集成到一塊芯片上,半導體制造工藝的進步使CMOS邏輯單元可以和SRAM或DRAM集成在一個硅片上,這樣可以突破芯片間引腳的限制,充分發揮存儲器的隱藏帶寬,同時降低訪問延時(將片間訪問延時轉換成片內訪問延時遲)。以PIM技術為基礎,用向量部件作為協處理器構成的Vector In Memory(VIM)體系結構,可充分發揮PIM高帶寬、低延遲、低功耗的特點,開發數據級并行,是解決存儲系統性能瓶頸的有效途徑。本文具體闡述VIM體系結構中影響存儲系統性能的關鍵部件嵌入式存儲控制器的設計與實現。

2 VIM體系結構

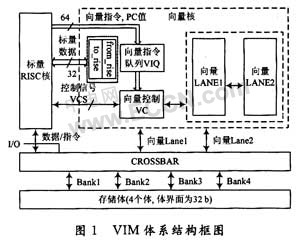

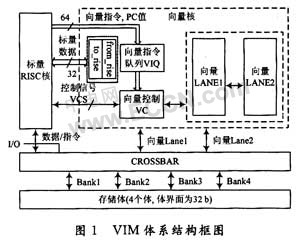

VIM是一種面向流式數據處理的向量體系結構,其微體系結構的處理器部分由1個標量核和1個向量協處理器構成,嵌入式存儲控制器和存儲器構成片上DRAM存儲系統,處理器部分和存儲系統之間由高速存儲交叉開關互連。VIM體系結構最重要的特征就是向量處理器和嵌入式存儲器的結合。圖1中給出了VIM系統結構的典型框架結構。

2.1 RISC標量核

VIM標量核為可綜合、高集成度的32位RISC處理核,其指令集與SPARC V8兼容;標量核包括整數部件、浮點部件,支持用戶態和超級用戶態(管態)2種工作模式;主要功能是執行標量指令(SPARC指令集),處理異常和中斷,為向量部件輸送向量指令,完成標量核與向量部件之間的數據傳遞,并與主機進行通信完成取指、譯碼工作。

2.2 向量部件

向量部件作為標量核的協處理器,執行擴展的向量指令,與標量部件并行執行。由向量指令隊列、向量控制器、向量核寄存器文件、向量Lane等部分構成。向量指令隊列VIQ,為異步FIFO隊列。標量核通過部分譯碼將識別出的向量指令寫入VIQ,由向量取指單元從中順序取出指令交由譯碼部分再次譯碼。向量控制器保證向量指令的正確執行,完成向量流水線控制。向量核寄存器文件由向量寄存器文件、標量寄存器文件、控制寄存器文件和標志寄存器文件構成,包括32個32位寄存器。向量Lane由并行的向量流水線構成,包括完全流水的LSU,ALU,FPU等部件。每個Lane可以看成一條數據通路,完成對特定寬度數據的處理,多個Lane之間可以并行執行。

2.3 嵌入式存儲系統及I/O

嵌入式存儲系統由存儲互連交叉開關、嵌人式存儲控制器和存儲器構成,存儲互連交叉開關用于片內運算部件訪存時的地址翻譯、訪存指令的路由以及讀取數據的返回,其將標量訪存部件、向量Lane訪存部件和嵌入式存儲器互連起來,具有多端口、高帶寬、低延時的特點。嵌入式存儲控制器接收從存儲交叉開關傳送過來的訪存指令,實現對DRAM的數據存取。存儲器是由4個獨立的存儲體組成的一個多體交叉存儲器,每個存儲體都有自己獨立的存取控制接口,體內又分成4個子體。采用多體存儲器可使映射到不同存儲體的訪存指令可以同時執行,并行對多個向量元素進行操作,同時每個存儲體都對應各自的存儲控制器,相對于集中式存儲控制而言訪問延時更低、功耗更小。I/O接口用于實現多個VIM節點間互連和掛接一些I/O設備。

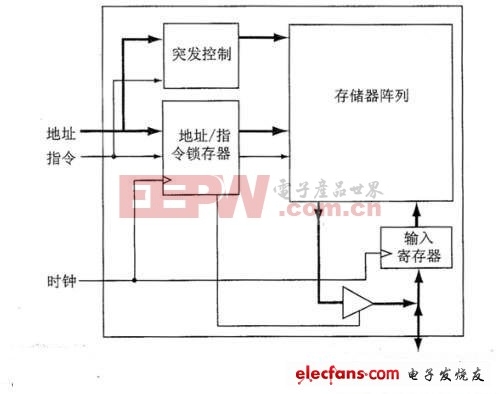

嵌入式存儲控制器實現對DRAM存儲體的初始化、激活、行選、列選、自動充電、定時刷新、讀延遲、寫恢復等功能控制,支持4種突發讀寫模式、兩種行選延時選擇,具有嚴格的時序。下面將詳細闡述嵌入式存儲控制器的設計方案,設計思想以及具體實現。

3 嵌入式存儲控制器設計與實現

3.1 嵌入式存儲控制器模塊結構

存儲控制器是系統總線和DRAM之間的控制接口,在VIM的存儲系統中,嵌入式存儲控制器的作用就是將存儲交叉開關所傳輸過來的讀寫控制命令轉換成DRAM的控制信號實現對DRAM的讀寫、刷新等控制;將存儲交叉開關傳輸過來的地址分解成Bank地址、行地址和列地址,在特定的時候傳輸到DRAM地址線上;以及控制數據總線和DRAM數據線的數據輸入輸出。

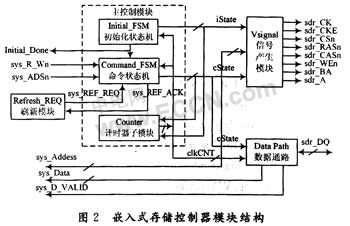

實現VIM-1嵌入式存儲控制器,圖2所示為其模塊結構,存儲控制器由主控制模塊、信號產生模塊、刷新模塊和數據通路構成。

下面具體對每個模塊的功能進行闡述:

存儲器相關文章:存儲器原理

評論