認知無線電:現場可編程射頻器件提供突破性的機會

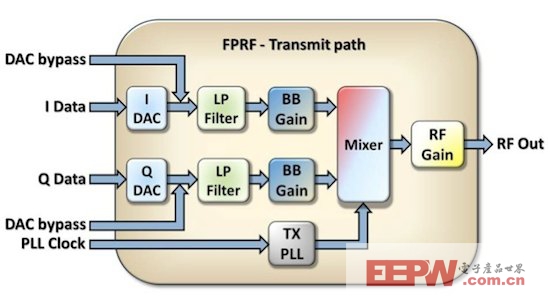

在發送側,基帶電路提供由流進DAC的IQ數據調制的射頻輸出。在收發路徑上芯片都有濾波器,這些濾波器可以針對各種不同帶寬進行編程。這樣就可以將信號限制在感興趣的帶寬內,并衰減掉由數據轉換器引入的不可避免的混疊和量化噪聲。每個放大器均可提供可編程的增益,同時芯片針對接收到的信號提供低噪聲放大器(LNA)選擇。器件可以通過串行接口(SPI)連接進行編程,因此操作非常方便快捷。

圖2:FPRF發送功能框圖。

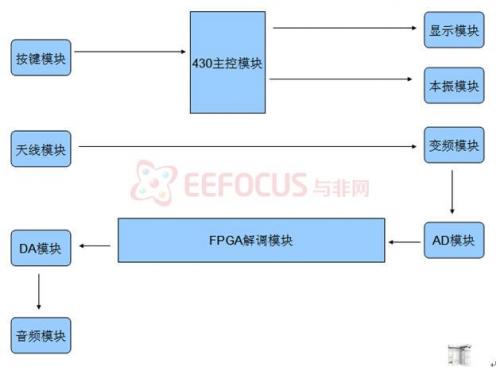

這份簡要說明應該介紹一下為什么Lime的FPRF器件適合認知無線電。這種器件能夠滿足靈活、頻率多變設備的低功耗和經濟性要求。在大多數應用中,數字處理和控制是由現場可編程門陣列(FPGA)完成的。

圖3:FPGA和FPRF為認知無線電系統提供了一個平臺。圖中由Nuand公司提供的電路板將Altera的FPGA和Lime的FPRF整合在一起。

圖3:FPGA和FPRF為認知無線電系統提供了一個平臺。圖中由Nuand公司提供的電路板將Altera的FPGA和Lime的FPRF整合在一起。

FPGA 可以用來解碼由FPRF芯片輸出的數字IQ數據,也可以用來編碼該數據進行發送。使用FPGA執行基帶功能的硬件加速任務的優勢是,它可以針對 沒有現成ASSP器件可用的演示系統進行設計,比如認知無線電系統這種情況。設計可以加以定制以適合系統,而且由于邏輯部分在操作期間可以進行動態重配 置,所以能夠實現某種復雜的硬件加速效果。例如,邏輯部分可以經過重配置產生IQ數據,進而在信道的信噪比較差時提供正交相移鍵控 (QPSK),或者在信號條件較好的情況下提供正交幅度調制(QAM)實現更快的數據傳送。即使低成本FPGA也有的另外一個優勢是,它們包含復雜的時鐘 管理模塊。這些模塊可以通過整合模擬PLL或數字鎖相環(DLL)提供頻率綜合和相移功能。低抖動時鐘發生和抖動濾波功能則可以用來產生時鐘,進而驅動 FPRF的收發PLL,滿足要求不太嚴格的應用需求。

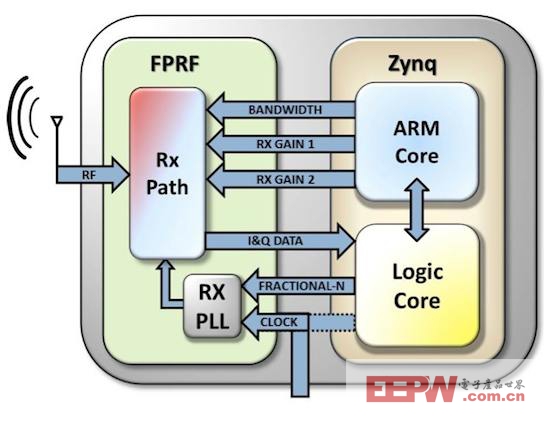

FPRF芯片邏輯和參數的重配置智能是由系統處理器上 運行的軟件提供的。賽靈思和Altera公司的器件都包含高性能ARM處理器,并作為硬件內核的方式嵌入在里面與可編程邏輯放在一起。這樣就有機會減少芯 片數量并提高系統性能。下面的文字描述介紹了將賽靈思的Zynq器件用作基帶芯片的概念。之所以選擇Zynq是因為在ARM和可編程邏輯之間有多條快速片 上連接和數據總線可提供高帶寬。另外,諸如Linux等操作系統(OS)支持、設計和調試工具以及用于設計可編程邏輯和ARM組合的全面支持生態系統也都 是現成的。

在認知無線電中,第一步操作是掃描空中電波是否有免費頻率。Zynq器件上的處理器按順序設置FPRF中的帶寬和 增益控制,并使用SPI接口加載寄存器(圖中為了看得清楚將它們顯示為單獨的路徑,實際在四線SPI上使用了時分復用技術)。ARM處理器和可編程邏輯內 核的組合用于通過SPI改變接收PLL上的小數N和頻率值。這樣就能讓Zynq經過所有信道,而接收到的IQ數據提供了信號的瞬時電平。可編程 邏輯一般用于處理來自FPRF器件的數據,ARM軟件可以被編程為暫停在信號低于預定義電平的任意信道上。如果需要的話,Zynq還能調整增益或帶寬以確 保信道沒有業務。需要的話,系統還能在整個過程中通過多次掃描來建立當前的業務圖案。

圖4:FPRF接收器在軟件控制下掃描免費信道,并鎖定到所選的頻率。

一旦狀態確定,認知無線電就能發送它所選擇使用的頻率、帶寬和調制方案,并且可能在專門針對這些數據的預定信道上發送。FPRF能夠支持全雙工操作,一旦在認知無線電的發送和接收端之間相互同意所用的收發信道、帶寬和調制方案,系統就能切換到這些設置。

評論