Rapid IO---成就高速互連之美

在過去的30多年時間內,處理器的主頻和性能呈現指數上升的趨勢,而與之相對應的處理器總線傳送能力的增長卻相對緩慢的多,這就導致了由時鐘頻率表征的CPU的性能和由總線頻率表征的CPU可用的總線帶寬之間的差距不斷在變大,互連總線成為高速運算和處理系統的瓶頸。現代的高性能計算系統和網絡存儲系統需要更高速率的數據傳送。高帶寬、低延遲,高可靠性成為衡量一個總線技術的基本要求。

本文引用地址:http://www.104case.com/article/258683.htm

一、 傳統總線的問題:

傳統總線多采用并線總線的工作方式,這類總線一般分為三組:數據線,地址線和控制線。實現此類總線互連的器件所需引腳數較多,例如對于64位數據寬的總線,一般由64根數據線,32-40根地址線以及30根左右的控制線,另外由于半導體制造工藝的限制還要加上一定數量的電源引線和地線,總共會有約200根左右的引線,這給器件封裝、測試、焊接都帶來了一些問題,如果要將這種總線用于系統之間的通過背板的互連,由此帶來的困難就可想而知。

為了提高總線的傳輸能力,傳統總線多采用增加數據總線的寬度或是增加總線的頻率的方式來實現。如PCI總線支持25M、33M、50M、66M的工作頻率,PCI-X總線是在PCI總線結構的基礎上進得到的一種總線結構,在硬件和軟件上兼容PCI總線,PCI-X總線可以支持32bit、64bit的總線,其工作頻率為66M、133M,對于64bit的PCI-X,如果其總線工作頻率為133MHz,其峰值傳送帶寬可達到133×64bit=8.512Gbps。目前PCI-X也有一些版本定義了總線頻率為266MHz或者533MHz的總線,另外也有一些總線定義了數據寬度為128bit 或是256bit的總線,但很少有人會選用這樣的總線,因為增加總線頻率和數據帶寬雖然一定程度上滿足了人們對高速數據傳送的需求,但同時也帶來了一些新的問題。更寬的總線導致器件引腳數的增加,從而增加封裝尺寸,當然帶來成本上的增加。

另一個問題是當總線的工作頻率超過133MHz時,很難在一條總線上支持超過兩個外部設備,在總線上增加器件相當于增加容性負載,而容性負載的增加意味著裝載或排空電荷使總線達到所需的額定電平的時間增長,信號的上升和下降時間的增長會限制總線的工作頻率。對于并線總線的另一個問題是時鐘與信號的偏移容限的問題,對于這樣一組并行信號線的集合,信號的采樣是取決于時鐘信號的上升沿或是下降沿,這樣對于信號的跳變和時鐘的跳變時刻的時間差就有一個上限值,隨著速率的升高,布線長度、器件門電路自身的翻轉時間都會影響總線的速率。

用于處理器之間互連以及背板互連的另一個主要技術是以太網,近些年來,以太網在存儲、電信、通訊、無線、工業應用以及嵌入式應用中得到大量的應用,現有的成熟的硬件和協議棧降低了開發的復雜性和產品的開發成本。但是在局域網和廣域網中得到很好應用的以太網用于這種芯片級或是板極的系統互連顯示出了低效率、高延時的特性,QOS需要高層軟件的參與,造成軟件模塊化結構不清晰。尤其是當背板的傳輸速率從1Gbps增加到10Gbps時,增加的處理要求已經超出了以太網的能力。

二、什么是Rapid IO?

Rapid IO技術最初是由Freescale 和Mercury 共同研發的一項互連技術,其研發初衷是作為處理器的前端總線,用于處理器之間的互連,但在標準制定之初,其創建者就意識到了RapidIO還可以做為系統級互連的高效前端總線而使用。1999年完成第一個標準的制定,2003 年5月,Mercury Computer Systems公司首次推出使用Rapid IO技術的多處理器系統ImpactRT 3100, 表明Rapid IO已由一個標準制定階段進展到產品階段,到目前為止,Rapid IO已經成為電信,通迅以及嵌入式系統內的芯片與芯片之間,板與板之間的背板互連技術的生力軍。

Rapid IO 是針對嵌入式系統的獨特互連需求而提出的,那么我們首先來說明嵌入式系統互連的一些基本需求:嵌入式系統需要的是一種標準化的互連設計,要滿足以下幾個基本的特點:高效率、低系統成本,點對點或是點對多點的通信,支持DMA操作,支持消息傳遞模式交換數據,支持分散處理和多主控系統,支持多種拓樸結構;另外,高穩定性和QOS也是選擇嵌入式系統總線的基本原則。而這些恰是Rapid IO期望滿足的方向。所以Rapid IO在制定之初即確定了以下幾個基本原則:一是輕量型的傳輸協議,使協議盡量簡單;二是對軟件的制約要少,層次結構清晰;三是專注于機箱內部芯片與芯片之間,板與板之間的互連。

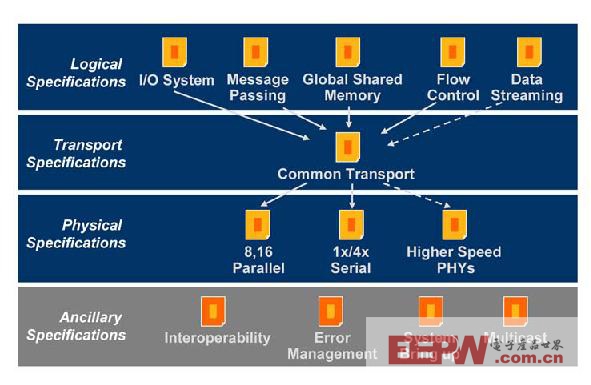

Rapid IO采用三層分級的體系結構,分級結構圖如下圖所示:

由此圖可見,Rapid IO協議由邏輯層、傳輸層和物理層構成。最明顯的一個特點就是Rapid IO采用了單一的公用傳輸層規范來相容、會聚不同的邏輯層和物理層,單一的邏輯層實體增強了Rapid IO的適應性。

物理層定義了串行和并行兩個實體,得到廣泛應用的只有串行方式,尤其是用在背板互連的場合,串行方式可以在兩個連接器之間允許80-100cm的連線,單鏈路傳輸帶寬可達10Gbps。目前Rapid IO的標準是Version1.3,在未來的Version2.0規范中定義了更高的傳輸速率,可以得到更高的傳輸帶寬。

物理層:

Rapid IO規范中定義的最低層是物理層,最初定義的是并行總線,之后定義了串行總線,并線總線可以選擇8位或16位的寬度,傳輸電平采用LVDS方式,時鐘信息在一對單獨的差分線上傳送,不在數據流中編碼,頻率在250M-1.0G之間。相比串行總線而言,無多少優點可言,所以只是在最初有支持這種總線的芯片出現,目前幾乎所有的物理層均采用了串行方式。

串行物理層定義了器件間的全雙工串行鏈路,在每個方向上支持1個串行差分對稱為1個通道(1x),或同時支持4個并行的串行差分對稱為4通道(4x),接口的電氣特性采用成熟的XAUI(10GbE Attachment Unit Interface)接口,編碼方式采用的是8B/10B編碼,對鏈路的管理,包括流量控制,包定界和錯誤報告等使用專用的8B/10B碼(即K碼),接收端從鏈路上提取時鐘信息,無需獨立的時鐘線。每一個通道支持三種不同的傳送波特率1.25G,2.5G,3.125G(與之相對應的數據速率分別是1.0G,2.0G,2.5Gbps)。

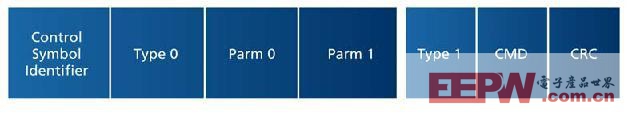

圖:Control symbol 包的結構

Rapid IO是一種基于可靠傳送的協議,每一個數據據包的傳送均要求對端在物理層上響應一個控制符號包,此包是一個4個字節的數據包,表明了數據包的傳送狀態,數據包是否被對方接方,還是要求重新發送或是包未被接收。發送方和接收方均可以使用控制符號包來獲得對方的狀態。

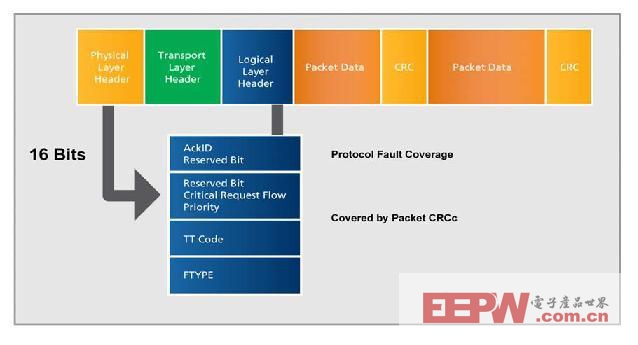

圖:Rapid IO包結構及物理層組成

評論