數字電源UCD92xx輸出電壓波形的優化

2.4 數字電源環路配置

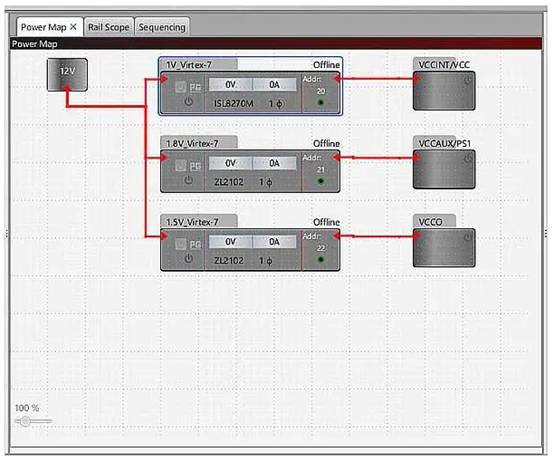

圖6和圖7是使用數字電源開發工具Fusion Digital Power Designer來配置環路的軟件截圖。該工具可以模擬整個環路并給出配置之后的閉環環路指標,包括截止頻率,相位余度和增益余度,極大的方便了環路的調試和優化。

圖6所示的是軟啟動時的環路配置。零極點的信息在“Linear Compensation”方框中,其中AFE的Gain設置為4×;該配置中使能了非線性增益,其Limit值和Gain值是允許用戶修改的。最終,整個環路的指標為23.87KHz(截止頻率),49.33°(相位余度),11.77dB(增益余度)。

圖7所示的是正常運行時的環路配置。零極點的信息在“Linear Compensation”方框中,其中AFE的Gain為4×;該配置中使能了非線性增益,其Limit值和Gain值是允許用戶修改的。最終,整個環路的指標為33.7KHz(截止頻率),50.57°(相位余度),8.77dB(增益余度)。

正是采樣上述配置,輸出電壓在軟啟動階段其波形有明顯的“臺階狀”。下面將嘗試放慢環路后,驗證是否可以優化軟啟動階段的波形。

2.5 優化環路配置

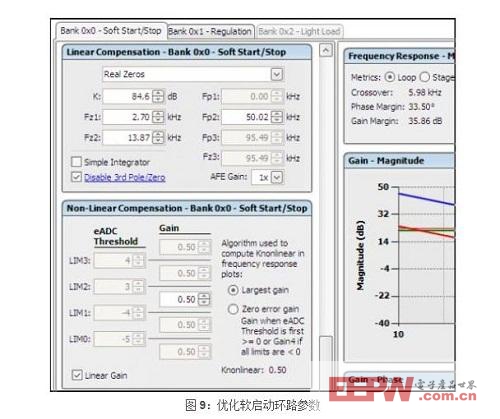

圖9是軟啟動環路優化后的軟件截圖。環路的優化包括:

1)不再使能非線性增益,同時將Gain0由1修改為0.5;這可以降低環路的低頻增益,最終降低環路帶寬;

2)將AFE的Gain由4修改為1,同樣可以降低環路帶寬。1倍的Gain將使AFE的輸出的精度變差,并最終影響到輸出電壓,但考慮到軟啟動階段對輸出電壓的精度要求略低,因此可以上述修改可以接受。需要說明的是,為保證正常運行時輸出電壓的性能(精度,動態性能等),正常運行時對應的環路參數將保持不變。

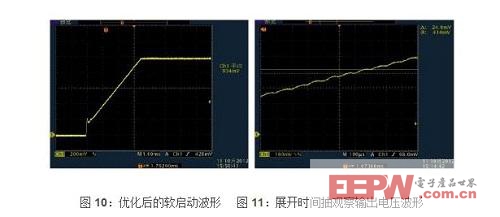

圖10所示的是優化環路后的輸出電壓波形,可以觀察到在軟啟動階段的“臺階”現象消失,波形平滑。

圖11是將時間軸展開后的輸出電壓波形,可以觀察到其步進的時間依然是100us,步進的幅度為24mV(與理論值25mV基本一致),但每一次的步進不再是突然增加,而是緩慢增加。因此,輸出電壓波形變得較為平滑。

但是,在圖10所示的波形中可以觀察到,輸出電壓在啟動時刻有一個正向過沖并很快回落。嚴格意義上,該過沖會影響輸出電壓波形的單調性,在一些應用場景中是不運行的。下文將針對該過沖進行優化。

評論