有關交錯ADC的更多觀點

作者:Jonathan Harris

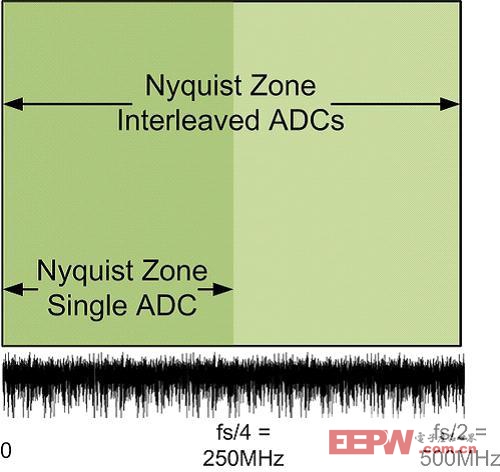

本文引用地址:http://www.104case.com/article/258386.htm交錯結構的優(yōu)勢可惠及多個細分市場。 最有用的優(yōu)勢是通過交錯ADC更寬的奈奎斯特區(qū)增加帶寬。 同樣,我們首先舉兩個500MSPS ADC交錯建立1000MSPS采樣速率的例子。 通過交錯兩個ADC,可以大幅增加帶寬。 注意,fS顯示的是一個轉換器;交錯轉換器采樣速率等于2 X fS。

它可以為各種不同應用提供優(yōu)勢。 很多設計中的內在系統(tǒng)要求都超前于商用ADC技術。 無論ADC采樣速率有多高,市場似乎都要求更高的速率。 交錯結構可填補技術空白。 軍事和航空應用正要求更高的帶寬,以實現更佳的空間識別能力。 此外,在后端通信中也需要增加通道帶寬。

就像蜂窩標準增加了通道帶寬和工作頻段數一樣,對ADC可用帶寬的要求也越來越高。 在某些市場和應用中,還出現了轉移到直接RF采樣的需求,這樣無線電設計的級數更少,并可移除解調器。 ADC具有足夠高的采樣速率還有可能降低時鐘要求。 因此,將ADC與DAC時鐘對齊便是可行的,從而簡化系統(tǒng)設計。 在儀器儀表和測量應用中,需要用到更高的帶寬,以獲取并測量信號。

更高的采樣速率能為這些應用提供更多帶寬。 它能使頻率規(guī)劃更輕松,并降低通常用于ADC輸入端的抗混疊濾波器的復雜程度和成本。

有那么多的優(yōu)勢,您一定會問這些優(yōu)勢的代價是什么。 就像大部分事情一樣,天下沒有免費的午餐。 交錯ADC具有更高的帶寬和其他有用的優(yōu)勢,但同時也帶來了一些挑戰(zhàn)。

我們能組合使用多少轉換器? 讓我們簡單看一下交錯ADC的時鐘要求:

m = 2時,此等式很容易求解。 然而,當m等于別的數(比如8)時,時鐘要求變得非常復雜。將m代入,并求解8個轉換器的等式,得到所需的時鐘相位為:0、45、90、135、180、225、270和315度。 若輸入時鐘頻率較低,那問題不大;但采用交錯結構的重點就是獲得高采樣速率。

實際情況中,時鐘頻率為1GHz。 這意味著時鐘電路必須要能劃分輸入時鐘,并創(chuàng)建相距125ps的相位;同時,還必須精確完成此操作。 時鐘的任何誤差或抖動都會降低性能。

評論